# Sem conductor

**Industry Association**

**Taiwan**

關鍵性產線零件及樣品

#### 最快班機、最短時間 - 美商世界速遞

全年365天、全天24小時的專業物流服務

#### 以下的狀況困擾著您:

- 1. 高科技廠的生產設備故障·極可能導致的生產線停擺· 進而 喪失重要合約、客戶與利潤?

- 2. 研發樣品寄送若無法準時導致除了喪失的重要合約,還 有 高額罰款/賠償?

- 3. 曾因 周末、國定假日、年節 無法寄送貨品嗎?

#### 請找世界速遞!

- 全球派送·服務網遍及全球200多個國家

- 專業客服人員為您解答有關 特殊物品/危險品運送 的 國際規則

- 可根據您的需求·不論畫夜·派遣專人送件或取件

- 除NFO (Next Flight Out) 服務 外·尚提供 Handcarry服務

- 無重量、尺寸、價值之限制

- 所有貨物均由 專人、專車及最快可用航班運送, 全程監控,直至送達

- 隨時提供運送過程中之即時動態報告,包括 電子郵件、網上查詢或電話通知

美商世界速遞有限公司台灣分公司 陳智宏 (Victor Chen) 02-2659-2866 / 0919-966-224 sales@worldcourier.com.tw

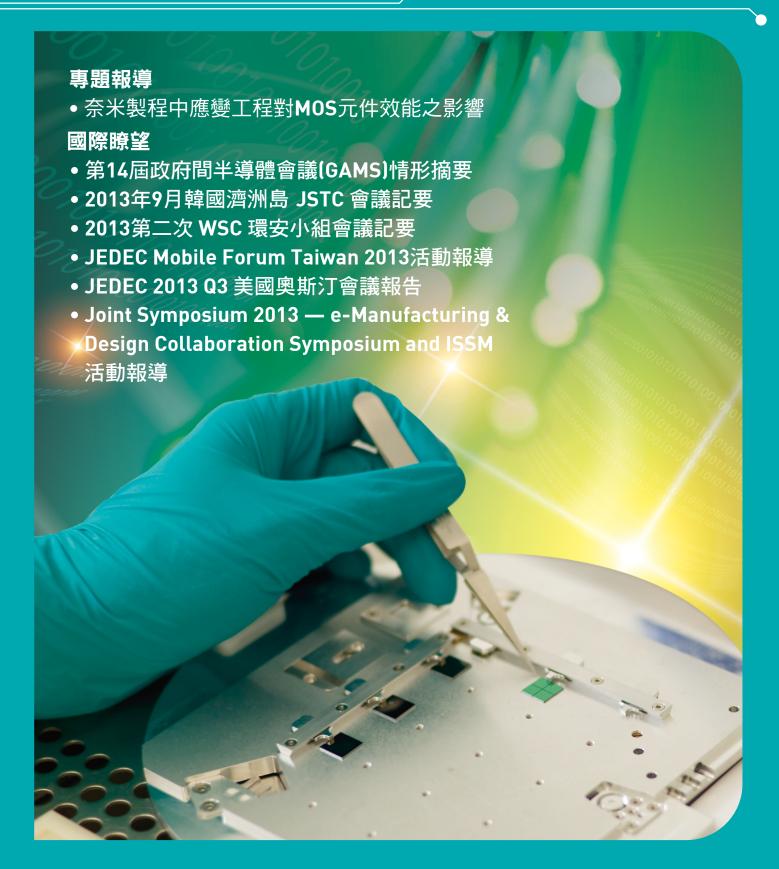

### VVGEM 把您的機上盒變成監控主機

DV3 11

監控連網機上盒

- 具即時監視與預約錄影功能,連接免設定

- 可同時收看節目與監視錄影,錄影後不需轉檔即可 直接在電視上觀看

- 費用平價,不需添購影像監控主機

- 錄影資料可存放至硬碟或外接USB儲存設備

- 支援Motion JPEG及H.264 MP4錄影儲存

- 可邊看DVB-T電視邊錄影,或上網、播放影片...

- 支援時段搜尋錄影檔案

- 獨家線上路況瀏覽,全省多個景點即時監看

- 可收看DVB-T數位電視節目

- 支援HDMI1080P輸出

#### ■ 瀏覽網頁、收發訊息

■應用程式下載

- ■影音播放中心

- ■支援多種影音格式

本國上市(興)櫃公司於2013年採用國際財務報導準則(IFRS),合併財務報表應按"集團"之概念編製,所有的具控制力的集團子公司均須納入合併的範圍,IFRS下"合併個體變動"乃為造成公司合併營收、淨利、現金流量以及淨值等大幅波動的主要因素之一;隨著企業投資行為越趨多元複雜,企業之某投資行為係對被投資方具實質經營權或是僅為代理第三方持有,將直接影響合併財報之正確,其判斷甚為重要!

2011年5月,國際會計準則委員會公佈了新的國際財務報告準則第10號公報(IFRS 10),取代原本兩個會計準則-第27號"合併和單獨財務報表"和SIC-12"特殊目的個體",10號公報對合併個體提出新的控制力評估模型,並且提供大量的新的應用指導和對權力的新定義。鑑於以往沒有專門針對投資基金經理人與其所投資之標的間之獨特關係做過規範,IFRS 10亦特別對此關係之合併標準提出詳細指引。本研討會希望透過解析公報對於判別委託人與代理人的案例解說,提昇與會者對於IFRS10控制力定義的了解。另,2011年5月國際會計準則委員會同步發佈IFRS 11(合資)及IFRS 12(未合併公司之揭露),係與IFRS 10整合為整套與投資活動相關之準則,亦將於此研討會一併介紹。

- 主辦單位:中華民國台灣半導體產業協會(TSIA)

- 協辦單位:安侯建業聯合會計師事務所(KPMG)

- 日 期:102年12月12日(星期四)13:30pm-17:00pm

- 地 點:交通大學電子資訊大樓第一會議室(新竹市大學路1001號)

- 費 用:TSIA會員,不限名額且免費參加;非會員費用:NTD3,000元整/人。

- 聯絡人:劉夢玲經理,Tel:03-591-3560,FAX:03-582-0056,e-mail:ccliu@tsia.org.tw

- 備註 1: 一律採網路線上報名方式,請至協會官網(http://www.tsia.org.tw)報名。

- 備註 2:交大停車費NT\$30/小時,請與會者自行吸收。

- 備註 3:名額為90位。研討會前三天將寄發報到通知與注意事項,敬請學員留意。

|             | Agenda                                                                            |

|-------------|-----------------------------------------------------------------------------------|

| Time        | Topic                                                                             |

| 13:30~14:00 | 報到                                                                                |

| 14:00~14:05 | 致詞 TSIA財委會主委/力晶科技 會計處處長 邱垂源                                                       |

| 14:05~15:35 | 『代理者 vs 委託者(主要經營者) - 談IFRS 10控制力實務議題,暨IFRS 11、IFRS 12介紹』(上)安侯建業聯合會計師事務所 黃海寧 執業會計師 |

| 15:35~15:50 | 休息                                                                                |

| 15:50~16:50 | 『代理者 vs 委託者(主要經營者) - 談IFRS 10控制力實務議題,暨IFRS 11、IFRS 12介紹』(下)安侯建業聯合會計師事務所 黃海寧 執業會計師 |

| 16:50~17:00 | Q & A                                                                             |

\*主辦單位得視情況保留變動講師、講題、議程、時間、場地之權利

#### 致各位業界先進

TSIA理監事會於2013年6月成立產學委員會,宗旨為協助會員善用學術界資源,以提升半導體產業的研發力與競爭力,促進產業與學界之互動交流,培養學生早期瞭解並參與半導體產業,促成青年才子以半導體產業為其終身事業。

目前產學委員會正在積極進行的工作計劃有:

- 一、半導體發展主軸計劃白皮書

- 二、企業領袖校園演講

- 三、產學基金募集

其中第三項「產學基金籌措」之目的為支付產學合作運作過程中之必要行政費用,如會議費、白皮書出版費用及未來陸續新增的產學合作計劃等。

歡迎各位業界先進支持與捐款,以利後續工作之推動。產學基金為專款專用,保管單位為 TSIA秘書處。

敬請填寫下列回函並回傳至03-582-0056或email至ccliu@tsia.org.tw,我們會儘快與您聯絡繳款事項,謝謝。

#### 【產學基金捐款回函】

致: 台灣半導體產業協會 劉夢玲 經理

Tel: 03-591-3560 Fax: 03-582-0056 E-mail: ccliu@tsia.org.tw

本公司願意捐助下列內容予「台灣半導體產業協會2014產學委員會產學基金募集計劃」

| 公司名稱   |                                    |      |                 |    |

|--------|------------------------------------|------|-----------------|----|

| 聯絡人/職稱 |                                    | 電    | 話               |    |

| E-mail |                                    | 傳    | 真               |    |

| 捐助內容   | □ 贊助款NT\$25,000<br>或<br>□ 贊助款NT\$( | (NTD | <b>25,000</b> i | 匙) |

2013 WSTS秋季預測會議將於2013年11月18-21日假台北晶華酒店舉行,11月19日(二)將提供一個給非WSTS會員觀摩的機會,若 貴公司有半導體end products,並有興趣了解WSTS data及參與WSTS,歡迎與協會聯繫,請聯絡TSIA-吳素敏資深經理(Tel:03-5913477; Email:julie@tsia.org.tw),如需WSTS詳細資料請上網: http://www.wsts.org/Teaser-Left/Introduction-to-WSTS或與協會聯繫。

#### 如果您不是WSTS會員,又需要參考WSTS Data,請看這裡!

### 世界最具公信力的 半導體市場需求面WSTS統計資料

為加強服務台灣及周邊部分亞太區非WSTS會員,TSIA已與WSTS簽署 Distribution License Agreement,代為銷售WSTS統計資料給無End Product & foundry之非WSTS會員,即日起,TSIA會員價NTD30,000元;非TSIA會員NTD60,000元,以服務會員廠商。意者請洽協會03-5913477吳素敏資深經理,或上網https://wsts.tsia.org.tw。

#### 亞太區銷售點

※代理銷售地區包括:

台灣、香港、中國大陸、馬來西 亞、印尼、菲律賓

※WSTS出版品包括:

☆藍皮書(Blue Book),每月出版

☆緑皮書(Green Book),每月出版

☆預測報告(Forecast Report),每

半年出版

☆年度報告 (Annual Report ),每年 出版

※年度費用:

TSIA會員價NTD30,000元

非TSIA會員NTD60,000元

世界半導體貿易統計協會(World Semiconductor Trade Statistics;簡稱WSTS) 己有37年歷史,1975年由美國半導體協會(SIA)創立,當年即有美國十大半導體廠商加入;1981、1984、1992、1995年分別有歐洲、日本、韓國、台灣主要半導體廠商先後加入,並由各地區的半導體協會協助會員業務聯絡及新

會員招募,如台灣區即由台灣半導體產業協會(TSIA)協助。至2002年WSTS的會員統計資料顯示,已含全球半導體90%的產出,據使用過此資料的會員表示,全球各分析機構的報告,以WSTS統計的歷史資料,最為準確,對未來市場產品的分析,最具參考性。

WSTS目前已有全球超過70家半導體廠商加入,依地理及產能分佈,全球分為美國區(含INTEL、AMD、IBM、TI、LUCENT、MICRON…)、歐洲區(含PHILIPS,INFINEON…)、日本區(含TOSHIBA、MATSUSHITA、NEC、SONY…)、亞太區以韓國、台灣為主(含SAMSUNG、HYNIX、VANGUARD、WINBOND、NANYA、MACRONIX…)等四大區。會員每月需按WSTS所規範的產品、產業及地理區域格式,填寫實際出貨數字,並依此每月出版藍皮書(Blue Book)、綠皮書(Green Book),

每季出版全球四大區域出貨資料, 每年出版產業應用及區域出貨分析 給各會員作為市場分析參考;並於 每半年在全球四大區域輪流召開半 年會,於會中檢討WSTS格式以因 應外界變化而隨時修正,並由會員 輪流作各區域的總體經濟分析,產 品及產業應用分析,並對下二年度 依每季的產品需求作出未來的預 測。WSTS半年會旨在對全球半導 體廠商做未來兩年全球半導體的預 測。在會議中,各半導體公司代表 針對不同的產品線,發表並交換 對未來預測的看法。經過熱烈討 論,達成共同的數字預測後,再對 外界發表。WSTS預測報告(Forecast Report)對公司之產業預測具參考價 值。另依據以上資料彙整出版年度 報告(Annual Report),亦深具參考 價值,歡迎訂購。

### contents 目錄

#### 台灣半導體產業協會簡訊 TSIA NEWSLETTER

NO.66 ▼ 2013 / October

創刊日期:中華民國86年7月

出版字號:新聞局版台省誌字1086號

發 行 人:盧超群總 編 輯:伍道沅

執 行 編 輯:陳淑芬 江珮君

編輯小組:吳素敏 石英堂 劉夢玲 黃佳淑

簽 行 所:台灣半導體產業協會

地 址:新竹縣竹東鎮中興路四段195號51館

1246室

網 址:http://www.tsia.org.tw/

電 話: (03) 591-3181 傳 真: (03) 582-0056 E - m a il: candy@tsia.org.tw

地 址:新竹縣竹北市光明六路301之3號4F

編 輯:有囍廣告有限公司

電 話: (03) 558-6363 傳 真: (03) 558-6362

電子書製作: 龍璟文化事業股份有限公司 地 址: 新北市中和區建一路176號13F

電 話: (02) 8227-2268 傳 真: (02) 8227-1098

#### 01 編者的話

#### 專題報導

**02** 奈米製程中應變工程對MOS元件效能之影響

王木俊教授 明新科技大學電子工程系暨

台北科技大學機電整合研究所

#### 國際瞭望

**08** 第14屆政府間半導體會議(GAMS)情形摘要

經濟部國際貿易局

**11** 2013年9月韓國濟洲島 JSTC 會議記要

陳淑芬協理/TSIA

| 5 2013第二次 WSC 環安小組會議記要

呂慶慧資深研究員/工研院

**7** JEDEC Mobile Forum Taiwan 2013活動報導

吳素敏資深經理/TSIA

21 JEDEC 2013 Q3 美國奧斯汀會議報告

宣敬業經理/聯發科技 邱濱棋經理/華邦電子

Joint Symposium 2013 — e-Manufacturing & Design Collaboration Symposium and ISSM 活動報導

石英堂資深經理/TSIA

#### 會務報導

**29** TSIA理監事會推動產業發展研討會花絮報導

黃佳淑經理彙整/TSIA

33 2013 TSIA IC 設計委員會會議暨IC設計之友夏季聯誼

餐會報導

吳素敏資深經理/TSIA

34 半導體智財價值策略研討會活動報導

吳素敏資深經理/TSIA

35 台灣半導體產業第三季回顧與展望

TSIA;工研院IEK系統IC與製程研究部

**37** 「IFRS實行對稅務之影響及給付國外報酬衍生之扣繳

議題」研討會活動報導

劉夢玲經理/TSIA

38 TSIA委員會活動摘要

黃佳淑經理彙整/TSIA

41 新會員介紹

編輯部

#### 遊憩人間

**43** 走吧, 江南style!

Che N

■本案聯絡人 吳素敏 資深經理 ■電話:03-5913477 ■傳真:03-5820056 ■E-Mail:Julie@tsia.org.tw

### 編者的話

**大**氣逐漸轉涼,先祝福會員朋友有個豐收的季末。

本期「專題報導」單元,由明新科技大學電子工程系王木俊教授分享「奈米製程中應變工程對MOS元件效能之影響」。王教授介紹了在半導體製程中,提升前段製程的電晶體開關效能與降低後段製程的導線電阻並雜散電容這兩大主軸。文中針對前者前段製程,尤其在應變工程上,作進一步解析製程與元件特性之相連性探討。

TSIA在下半年仍積極參與了各項國際會議與活動,包括2013年8月15日在台舉辦JEDEC行動裝置高峰論壇 (JEDEC Mobile Forum)、9月6日於新竹國賓舉辦e-Manufacturing & Design Collaboration Symposium 2013; 並參加9月9-13日於美國奧斯汀舉辦之JEDEC 2013 Q3會議、及9月23-27日在韓國濟州島舉辦之GAMS/JSTC 會議與WSC環安小組會議等,本期「國際瞭望」單元皆有詳細報導。

繼上一季「TSIA理監事會推動產業發展研討會」獲得熱烈迴響後,9月27日再次舉辦第二場,以當前國際競爭局勢正在改變,跳脫本位迷思由外商角度來看台灣半導體產業競爭中之機會、威脅及優劣勢分析為主題,現場討論熱絡,活動圓滿成功。另外,台灣半導體產業第三季回顧與展望、半導體智財價值策略研討會、IFRS實行對稅務之影響及給付國外報酬衍生之扣繳議題研討會等活動報導,及各委員會活動摘要與新會員介紹等,請參考「會務報導單元」。

近期,TSIA將於11月18-21日假台北晶華大酒店舉行WSTS秋季預測會議,誠摯邀請大家踴躍參與,活動詳情與報名辦法請密切注意協會網站http://www.tsia.org.tw所發佈之訊息。

- 1.本簡訊歡迎您的投稿,文章主題範疇包含國內外半導體相關產業技術、經營、市場趨勢等。內文(不包含圖表) 以不超過四千字為原則,本刊保留刪改權,若有意見請特別聲明。

- 2.來稿歡迎以中文打字電腦檔投稿,請註明您的真實姓名、通訊處、聯絡電話及服務單位或公司,稿件一經採用,稿費從優。

- 3.本簡訊歡迎廠商刊登廣告,全彩每頁三萬元,半頁一萬八千元。

會員廠商五折優待。意者請洽:江珮君 03-5913181或email至: candy@tsia.org.tw

p EATURE ARTICLES 事 題 報 導

### 奈米製程中應變工程對MOS 元件效能之影響

王木俊教授

明新科技大學電子工程系暨台北科技大學機電整合研究所

#### 前言

隨著電子科技的進步,人們對於現有的IC產品常是不會滿足的。為此緣由,也提供整個半導體產業鏈,從IC設計、製造、測試與封裝等四大領域的工程師或研究人員,一直往前邁進。不管是新的IC設計架構提出、製程能力提升、相關製程與測試設備的改善或封裝技術的突破,在在都是為了消費者的需求。所有的電子產品,一般皆以輕、薄、短小、省電、省錢並快速操作為原則。為了符合此目標,在半導體製程中,主要以提升前段製程的電晶體開關效能與降低後段製程的導線電阻並雜散電容為兩大主軸。本篇文章將針對前者前段製程,尤其在應變工程上,作進一步解析製程與元件特性之相連性探討。

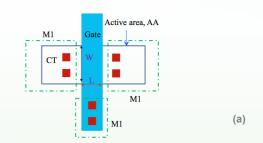

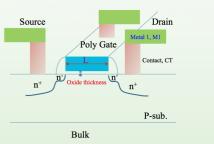

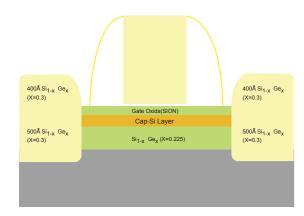

#### I. MOS元件效能的提升

對於奈米等級之MOSFET(Metal-oxide-semiconductor field-effect transistor, 金氧半場效電晶體)元件而言,影響其元件效能的主要因素,大致可由下面幾個公式加以說明,而為了簡化說明,在此以電子通道MOS元件(n-channel MOSFET, nMOSFET)為例子[1],其示意圖如圖1所示:

$$I_{DS} = \frac{W}{2L} \cdot \mu \cdot C_{ox} \cdot (V_{GS} - V_T)^2 (1 + \lambda \cdot V_{DS})$$

(1

$$V_T = \phi_{ms} - \frac{Q_f}{C_{or}} - \frac{Q_d}{C_{or}} + 2\phi_F \tag{2}$$

$$\phi_F = \frac{kT}{q} \cdot \ln\left(\frac{N_a}{n_i}\right) \tag{3}$$

其中 $I_{DS}$ :源/汲極之飽和電流(Source/Drain (S/D) saturation current)、W:通道寬度、L:通道長度、 $\mu$ :漂移率(mobility)、 $C_{ox}$ :單位面積之電容值、 $V_{GS}$ :閘/源極之電壓差、 $V_T$ :門檻電壓 (Threshold voltage)、 $\lambda$ :通道調變因子(Channel length modulation factor)、 $\Phi_{ms}$ :金屬閘極與矽基底(Substrate)之功函數差、 $Q_f$ :閘極氧化層單位面積之電荷總合、 $Q_d$ :通道中單位面積之空乏電荷、 $\Phi_F$ :通道電荷反轉所需之電位、k:Boltzmann常數、T:元件操作時之絕對溫度、 $Q_f$ :單位電荷、 $Q_f$ :通道未操作時之絕對溫度、 $Q_f$ :單位電荷、 $Q_f$ :通道未操作時之絕對溫度、 $Q_f$ :可之本質 濃度(Intrinsic concentration)。

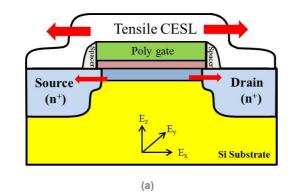

圖1. 簡易nMOSFET示意圖:

(a)佈局1P1M(1層poly-gate與1層metal layer)正視圖與

(b)剖面圖。

■ 台灣半導體產業協會簡訊 NO.66 October ■2

題 報 導

一般而言, $I_{DS}$ 值的增加,意味著MOS元件的開關速度也會增加,使得整體IC的效能也會有所提升,在全球市場的競爭力也因而有所俾益,對公司的獲利也相對地有所貢獻。瞭解此關聯性後,要使 $I_{DS}$ 值的增加,可以變動的參數顯示於公式(1)中,降低通道長度L的方法有微影製程作元件尺寸微縮並搭配蝕刻製程一齊使用;對於調變 $C_{OX}$ 值而言此變數亦可寫成:

$$C_{ox} = \frac{\varepsilon_o \cdot k}{T_{ox}}$$

(4)

其中  $\epsilon$ 。: 真空中之容電係數 ( vacuum permittivity)、k:相對性介電係數與 $T_{ox}$ :閘極介電質之厚度。

在增加CadL,可採用降低閘極介電質之厚度 或使用高介電係數(High-k, HK)的介電質(諸如HfO。 或ZrO<sub>2</sub>)。當以純SiO<sub>2</sub>作為閘極介電質,其T<sub>ax</sub>值降 低約至20Å時<sup>[2]</sup>,閘極之漏電流已大於最大可容忍 的限制1A/cm<sup>2</sup>,已無可下降的空間。在90奈米製程 點時,HK材料尚未完全成熟被導入製程整合中 時[3], SiON(Oxy-nitride)材料是一個不錯的選擇, 其k-value介於3.9至7.2之間, 暫時解決HK材料尚未 完全成熟的窘態。由於T<sub>x</sub>變薄,使得操作電壓(V<sub>cc</sub>) 也不得不縮小,除了維持正常操作電場(=V<sub>cc</sub>/T<sub>ox</sub>)約 5MV/cm ±10%的要求外, Vcc的縮小也意味著功率 消散(Power consumption與Vcc²成正比)的降低, 有助於IC散熱問題的解決,但不利於Ins值的提升, 為此 $V_T$ 值即必須縮小。在32奈米製程時,Intel公司 即把行之多年的閘極多晶砂(Poly-gate)改為金屬閘 極,一方面可調整nMOSFET或pMOSFET之功函數 差以得到較低的|VT|值外,也因使用金屬(諸如AI)作 為閘極材料,閘極之RC延遲問題可獲紓緩,並閘極 材料造成的功率消散問題,也可降低,可是製程的 複雜度提高許多,這會強烈地衝擊半導體廠整體晶

片產能(Throughput)與良率(Yield)穩定的控制能力, 是有必要作深入評核。

最後一項可變動的因子即是漂移率。對於電子 載子於nMOSFET通道傳輸時,其移動速度(v)與電 場(E)的關係式如下所示:

$$\nu = \mu_n \cdot E$$

(5)

$$\mu_n = \frac{q \tau_n}{m_n^*} \tag{6}$$

其中 $\mu_n$ 為電子之漂移率, $\tau_n$ : 平均碰撞時間 (Mean free time)與 $m_n^*$ : 電子之有效質量(Effective mass)。

漂移率與載子移動時所造成的散射(Scattering)或碰撞有密切的關聯。散射機率增加意味著載子的動能有所轉移,平均碰撞時間降低,因此載子的速度即會下降。對於電子於nMOSFET矽通道傳輸時其mn°=0.26 m。(mo:電子之靜止質量=9.11x10<sup>-31</sup> kg)對於電洞(Hole)於pMOSFET矽通道傳輸時其mp°=0.39 mo。電子與電洞於室溫下之漂移率,如表1所示[4]。

表1. 三種不同基底在低摻雜下之電子與電洞於室溫下之漂 移率。

|                                | Si   | Ge   | GaAs |

|--------------------------------|------|------|------|

| $\mu_n$ (cm <sup>2</sup> /V-s) | 1400 | 3900 | 8500 |

| $\mu_p$ (cm <sup>2</sup> /V-s) | 470  | 1900 | 400  |

對於矽原子,其最外層的電子軌域屬於3S²與3P²,對於3S與3P軌域以量子觀點而言,其相對應的能階很接近,因此有軌域混成(Orbital hybrid)的現象產生。當nMOSFET通道有拉伸現象(Tensile effect)時,相當於通道中晶格的距離變大些,使得電子載子所受到的碰撞機會降低些,又因為拉伸的擾動,也使在導電帶(Conduction band)的有效能量狀態密度(Effective energy state density)降低,因此其電子有效質量也因而降低些<sup>[5]</sup>。但對於電洞載子而

言(可視為電子的補位),若pMOSFET通道有壓縮現象(Compressive effect)時,因距離壓縮,因此補位更容易,使得電洞載子傳輸更快速些;另一方面,因有通道壓縮現象,在價電帶(valence band)的輕電洞(Light hole)較易被顯露,其影響傳輸比重電洞(Heavy hole)更明顯些,使得整體有效質量有降低的趨勢[6.7]。

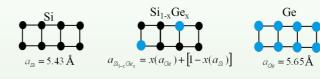

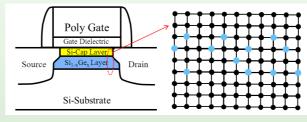

#### Ⅱ. 應變製程

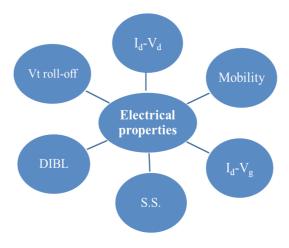

當瞭解應變機制如何影響電子或電洞在通道中 的傳輸後,即可著手於製程的改善。常見有兩種主要 應變製程稱為全面應變(Global strain)或稱為雙軸應 變(Biaxial-strain),此乃使用矽鍺虛擬為基板(亦即在 矽晶片表面沉積一層矽鍺薄膜以形成MOSFET元件) 以造成x軸與y軸皆有應變產生,此先驅研究以MIT與 Stanford研究團隊為代表。由於矽晶體的晶格常數為 5.43Å比緒晶體的晶格常數5.65Å小,當在矽晶體中 有鍺原子取代部分矽原子時,即有應變現象產生,而 鍺原子取代量的多寡將決定矽晶體中的應變程度(例 如20%的鍺原子在矽晶體中可以有0.8%左右的雙軸 拉伸應變產生),如圖2與3所示[2]。為了防止鍺原子(熔 點:936°C)在閘極熱氧化時,因高溫(約950~1050°C) 而擴散至閘極氧化層,因此常有一層矽覆蓋層(Sicap layer)作沉積,除了作為阻障層,並且因是純砂, 熱成長的閘極氧化層品質也較好。

圖2. 矽鍺晶體之晶格常數示意圖。

圖3. 通道中矽鍺薄膜與矽覆蓋層之示意圖。

基本上全面應變製程對nMOSFET與pMOSFET 元件在漂移率上,皆有不同程度的助益。由於晶片表面仍然呈現完整的矽晶格,以至於可成長高品質的閘極氧化物,在後續製程上可與MOS製程相同,因此可直接應用於產品上。只可惜,使用矽鍺基板為通道,由於應變矽與矽鍺仍是異介質接面,促使V<sub>T</sub>不易控制的問題;另外,對於提升pMOSFET效能而言,需要較高的鍺濃度,除了提高製程成本外,元件在中高垂直電場的操作下,也有漂移率退化(Mobility degradation)的問題被發現。由於此等不利因素,在量產考量上,即不再採用之。

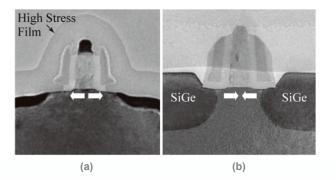

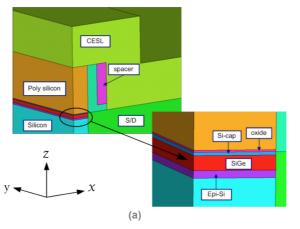

另一種應變製程稱為局部應變(Local strain)或 單軸應變(Uniaxial strain)。可利用特殊製程單獨對 nMOSFET或pMOSFET產生應變,如圖4所示。

圖4. Intel 90nm節點利用應變矽技術於(a)nMOSFET與(b) pMOSFET<sup>[2]</sup>。

在不同的奈米節點製程,所採用的應變技術也不一樣,如表2所示。在此,將對一般主要的局部應變技術作一介紹,包括:氮化矽接觸蝕刻停止層(Contact etch stop layer, CESL)沉積、金屬矽化物(Silicide)沉積、源/汲極重填(Refilled S/D with SiGe or SiC)、淺溝渠隔離(Shallow trench isolation, STI)製程、應力記憶技術(Stress memorization technique, SMT)與32或28nm節點採用閘極後製程(gate-last process)中的金屬閘極取代(Replacement

FEATURE ARTICLES 專 題 報 導

專 題 報 導

metal gate, RMG) 技術。在表3中,將此等局部應 變技術作一整理,以釐清何種製程對nMOSFET元 件或pMOSFET元件有利。

對於CESL應變膜(註:本來是作為接觸窗蝕刻之終點偵測,後來增加其沉積厚度,以形成對元件通道有應變功效),其薄膜沉積方式目前常用有兩種:低壓化學氣相沉積法(Low-pressure chemical vapor deposition, LPCVD)與電漿增強型化學氣相沉積法(Plasma-enhanced CVD, PECVD)。一般LPCVD沉積的CESL薄膜為拉伸應變,而PECVD沉積的為壓縮應變(但非絕對,也與其成長環境溫度、壓力氣體與濃度等有一定程度的影響)。當CESL薄膜x-方向為拉伸應變時,對於短通道元件而言,其x-方向通道應變也常是拉伸應變;但對於長通道元件,此種現象可能相反,而成為壓縮應變通道,如圖5所示[8]。

#### 表2. 國際各大廠及學術機構在局部應變製程之研究[2]。

| 公司         | 技術節點<br>(閘極長度)                      | 應變機制                                                                                                              | 遷移率 (電流) 増強                                                                                                                                                        | 參考文獻                                    |

|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Intel      | 90nm<br>(45nm for N,<br>50nm for P) | P: SiGe in S/D<br>N: Si <sub>3</sub> N <sub>4</sub> capping layer                                                 | I <sub>dlin</sub> >50%, I <sub>dsat</sub> >25% (P)<br>I <sub>dsat</sub> ~10% (N)                                                                                   | IEDM2002<br>p. 61<br>IEDM2003<br>p. 978 |

| TSMC       | 130nm<br>(90nm)<br>65nm             | Process-strained Si<br>(PSS): Cap layer, STI,<br>Silicide, STI                                                    | $I_{\text{off}}$ - $I_{\text{on}}$ @ 1V(P,N) ↑ 15%<br>$I_{\text{dsat}}$ 30%, $I_{\text{dlin}}$ ↑ 45% (P)<br>Mobility ↑ 45%<br>$I_{\text{dsat}}$ 35%(N) FinFET like | IEDM2003<br>p. 73<br>VLSI2003<br>p.137  |

| AMD        | (25nm)                              | Local Strain: Silicide,<br>Metal Gate, Spacer                                                                     | Electron mobility † 22% (simulation)                                                                                                                               | IEDM2003<br>p. 445                      |

| IBM        | 90nm<br>(45nm)                      | STI                                                                                                               | NA                                                                                                                                                                 | IEDM2003<br>p. 77                       |

| Toshiba    | (40nm)                              | SiGe/Si mismatch<br>lattice & STI                                                                                 | Mobility $\uparrow$ 33% (P) & Mobility $\uparrow$ 107% (N) by $L_g=1\mu m$ $I_{dsat}$ $\uparrow$ 11%~19% (P)                                                       | IEDM2003<br>p. 65                       |

| Mitsubishi | (55nm)                              | Poly+As => channel tensile                                                                                        | I <sub>d</sub> ↑ 15% (N)                                                                                                                                           | IEDM2002<br>p. 27                       |

| Hitachi    | 70nm                                | Si <sub>3</sub> N <sub>4</sub> cap+Ge implant<br>P-SiN: compressive<br>(PECVD)<br>T-SiN: Tensile<br>(Thermal-CVD) | I <sub>d</sub> ↑ 20% (N&P)                                                                                                                                         | IEDM2001<br>p.433                       |

| IMEC       | 250nm                               | Silicide (S/D & Gate)                                                                                             | $W_{S/D} \uparrow g_m \uparrow$                                                                                                                                    | IEDM1999<br>p.497                       |

#### 表3. 局部應變製程對n/pMOSFET之影響。

|      | nMOSFET                                            | pMOSFET                                               |

|------|----------------------------------------------------|-------------------------------------------------------|

| 拉伸應變 | Sic in S/D zone;<br>tensile CESL;<br>SMT; silicide |                                                       |

| 壓縮應變 |                                                    | STI; RMG;<br>SiGe in S/D zone;<br>compressive<br>CESL |

圖5. 局部應變矽之拉伸應力變化於:(a)短通道(b)長通道示意圖。其中 $E_x$ 、 $E_y$ 與 $E_z$ 為電場方向。

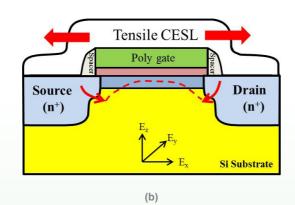

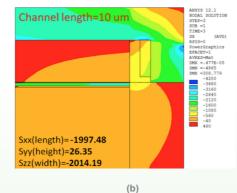

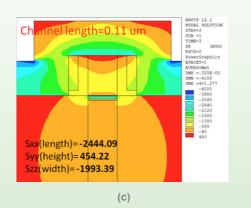

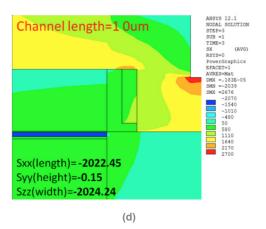

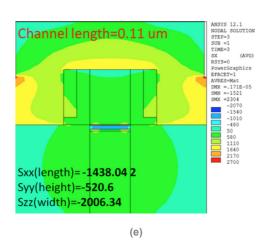

除了量測元件電特性分別外(如圖6所示),以探討應變矽製程是否真的對MOSFET元件效能有所提升,也常使用模擬軟體(例如:ANSYS software)以瞭解元件各區域所受的應力(Stress)<sup>[9]</sup>,如圖7所示。元件愈小,所受拉伸或壓縮應變效應愈明顯。

圖6. 應變製程調變後需注意之元件電特性變化示意圖。

圖7.90nm應變矽下之元件模擬:(a)元件構成圖、(b)長通道元件在壓縮應變下之應力分佈圖、(c)短通道元件在壓縮應變下之應力分佈圖、(d)長通道元件在拉伸應變下之應力分佈圖與(e)短通道元件在拉伸應變下之應力分佈圖。

對於金屬矽化物,例如:CoSi<sub>x</sub>, NiSi<sub>x</sub>, TiSi<sub>x</sub>, WSi<sub>x</sub>) 沉積產生的應變,主要乃因接觸窗(Contact)附近的材料,因熱脹冷縮係數不同所引起的,此種對於通道應變貢獻較小。在源/汲極重填(Refilled S/D with SiGe or SiC)技術方面,在nMOSFET可蝕刻掉原先以矽為主的區域,改填入以SiC為主的重掺雜區塊,因碳的晶格常數比矽小很多,在退火後,對通道可產生拉伸應力,唯碳容易在製程腔體(Chamber)中,產生污染,降低產品良率,因此較不被廣泛使用;但對於pMOSFET中,採用源/汲極矽鍺重填,對通道以產生壓縮應變,則能被普遍接受。又為了降低接觸阻值,也常讓此源/汲極矽鍺重填的高度比原來矽晶片表面來得高些<sup>[10]</sup>,如圖8示。對於SMT應變<sup>[11]</sup>乃利用閘極端的膨脹讓通道產生

應力並且記憶起來一般對於通道產生拉伸效應。當有STI製程產生應變時,對通道區域而言,會伴隨著壓縮應變的產生。一般而言,長通道之元件受影響不是很明顯,但當元件縮小後,此效應則相當明顯。在32或28nm節點採用閘極後製程時當S/D退火完成後,去除原先的多晶矽閘極,改回填低阻值係數的鋁金屬,此時會對pMOSFET元件的通道,產生壓縮應變稱為RMG應變技術。

圖8. 源/汲極矽鍺重填之元件剖面示意圖。

#### Ⅲ. 應變元件之可靠性探究

應變工程雖然提升了元件效能,但也可能使元件的可靠性變得很不好,這是需要注意的。常見需要作元件可靠性驗證的方法包括: 閘極氧化層的品質測試(Time-dependent dielectric breakdown, TDDB or time-zero ramping dielectric breakdown)、熱載子測試(Hot-carrier stress test)[12]與偏壓不穩定測試(negative or positive bias instability test)。電遷移測試(Electro-migration test)與應變工程的相關性較弱,一般在此等製程變動時,是暫不予以考慮。

#### IV. 結語

隨著元件尺縮小至奈米等級後,元件效能要繼續提升或保持不墜,是愈來愈不容易達成的。再加上製程成本的考量,能變動的參數著實不多。當應變工程此時被提出,實是令人欣悅。經過多方驗證,局部應變工程可被整合於CMOS製程主流中,即使製程進入20奈米或更先進製程,例如:結合鰭

式電晶體(FinFET)仍可被採用,因元件愈小,在元件上有些機械應力愈強,造成的應變也愈顯著,但卻使得元件模型(Device model)的建立愈困難。另一方面,即是可靠性的問題可能越嚴重,這皆須製程整合團隊在做整合時,作一全盤考量。

#### 參考文獻

- 1. Ben G. Streetman and S.K. Banerjee, Solid State Electronic Devices, 6<sup>th</sup> Ed., Prentice Hall, New Jersey (2006).

- 2. 鄭晃忠與劉傳璽:新世代積體電路製程技術,東華書局 (2011)。

- 3. Hong Xiao, Introduction to Semiconductor Manufacturing Technology, 1<sup>st</sup> Ed., Prentice Hall, New Jersey (2001).

- Chenming Hu, Modern Semiconductor Devices for Integrated Circuits, 1<sup>st</sup> Ed. Pearson Education, New Jersey (2010).

- S. Takagi, et al., "Comparative study of phonon-limited mobility of two-dimensional electrons in strained and unstrained Si metal-oxide-semiconductor field-effect transistors," J. Appl. Phys., vol. 80, 1567 (1996).

- K. Rim, et al., "Enhanced hole mobilities in surfacechannel strained-Si p-MOSFETs," IEDM Tech. Dig., 517 (1995).

- 7. 黃廣禮,"矽鍺半導體材料的物理特性與成長技術",電 子月刊 (2009)。

- L. Y. Kuo, et al., "The impact of uniaxial strain on low frequency noise of nanoscale PMOSFETs with e-SiGe and i-SiGe source/drain," IEEE IMS Digest, 23 (2010).

- 9. 徐鴻文, "Relationship between stress distribution and hot-carrier effect for nMOSFETs with CESL stressor", 博士論文,台北科技大學機電所 (2013)。

- 10.M.C. Wang et al., "Embedded SiGe source/drain and temperature degrading junction performance on <110> 45 nm MOSFETs," IEEE INEC, 1 (2011).

- 11.K. Bae, et al., "Behaviors and physical degradation of HfSiON MOSFET linked to strained CESL performance booster", IEEE IRPS, 852 (2011).

- 12.W.S. Liao, et al., "Drive current and hot carrier reliability improvements of high-aspect-ratio N-channel fin-shaped field effect transistor with high-tensile contact etching stop layer," APL, vol. 99, 173505-1 (2011).

### 第14屆政府間半導體會 (GAMS)情形摘要

經濟部國際貿易局

第14屆GAMS會議於本(102)年9月26日在韓國濟州島舉行,主要針對本年5月世界半導體產業協會(WSC)在葡萄牙里斯本舉行之第17屆年會中,產業界所提出對各國政府的建議進行廣泛討論,內容包括智慧財產權保護、自由開放市場、共同保護全球環境、衝突礦石及區域振興經濟等多項議題。我國除針對產業界關切之議題,事先透過雙邊會談之方式,與美、歐等國進行溝通外,並積極參與會議討論,以利GAMS會議達成有利我國產業發展之結論。

未來政府將持續與業界(中華民國台灣半導體產業協會)充分合作,透過此一重要國際平台,改善半導體 產業之國際經營環境並促進產業成長。本屆相關會議討論情形如下:

#### 一、雙邊會談

本次GAMS會議前,我方分別與美國貿易代表署副助理貿易代表Barbara NORTON及歐盟執委會貿易總署Petros SOURMELIS處長進行雙邊會談,相關重點如下:

#### (一)美國

我方首先就WSC提出希望GAMS成員間針對加密許可及認證程序議題於明(103)年GAMS會議前召開貿易官員及政府資訊安全專家會議之建議,詢問美方看法,並說明我方認為有必要進一步瞭解業界主要的關切內容,方能釐清應由哪些權責機關參與並進行實質的討論。美

方亦與我方持相同看法,同時提及TPP在法規調和議題中已納入類似的加密原則(列於ICT附件)。另關於WSC關切之美國加州「加強消費品安全法規」將於本年10月1日生效,其中對業者影響最大之禁用化學品清單尚未定案事,我方亦詢問美方相關進展,美方回應表示對於清單何時公布與具體內容尚無相關資料。

另針對我國業者反應自美國進口戰略高科技貨品後再出口時,取得美國政府同意文件不易且程序複雜冗長事,我方亦特別利用此次會談向美方表達盼相關申請程序可更加明確、透明化並縮短審查時程,且我國政府採認之ICP廠商盼能參加美國EXBS計畫之相關訓練課程。美方請我方提供我國過去就本案與美方之聯繫窗口,並允諾協助轉達我方關切與需求。

#### (二)歐盟

雙方主要就本次GAMS會議關切重點交換意見,歐方並就其無法同意支持WSC之貿易創新政策原則事預先向我國說明其立場。另我方亦利用本次會談瞭解歐方對加密議題的看法及相關負責的機關,歐方表示本議題係由歐盟執委會DG CONNECT及DG TRADE負責。

#### 二、我國政府代表與產業界代表工作 餐會

我業者除說明產業界討論最新進展外,並 表示WSC規劃針對半導體產業之碳排放計算機 制協調一共識版本,我國並獲選主導該議題, TSIA表示希望政府能委由智庫與產業界合作, 與GAMS成員共同推動對我有利之版本。另 WSC針對專利品質議題與WIPO之合作進展順 利,此次會議期間並與WIPO進行視訊會議, 我TSIA將輪值WSC IP委員會主席,繼續推動 與WIPO之合作,加以明年WSC年會將由我國 主辦,我方應可善用此機會加強與國際間在智 慧財產權保護領域之合作。

#### 三、GAMS會議

#### (一)智慧財產權保護

本次會議討論重點包括新型專利、專利品 質、營業秘密、反仿冒及非專利業者等議題。 其中針對WSC希望GAMS推動全球新型專利法 規調和之建議,美方及我方均對促進法規調和 表達正面之看法,惟因歐盟及中國大陸均認為 推動時機尚不成熟,爰GAMS決議僅對WSC未 來能提供更具體的建議表示歡迎。另我方並於 會中說明我國對新型專利之保護不會出現業界 所關切,對較低程度創新提供與發明專利相同 保護程度之情形。

另GAMS同意透過國內法規及洽簽貿易協 定等方式,進一步加強對營業秘密之保護,美 方並補充說明TPP已納入營業秘密章節,我方 則說明為加強對營業秘密之保護,我國已於今 年2月修正營業秘密法,對侵權行為課以刑事 責任。另針對專利品質及非專利業者(NPEs) 議題,GAMS決議除對WSC持續與WIPO合作 表示支持外,考量NPEs議題的複雜性與重要 性,以及本次會中美方就其處理NPEs議題情形 提出報告有助GAMS成員間對此議題之討論, GAMS除鼓勵其他成員後續亦能就NPEs的可能 影響進行檢視外,並希望WSC可以針對如何規 範包括非專利業者在內之專利所有權人濫訴問 題提出建議。

#### (二)自由開放市場

本議題主要針對WSC之加密、全球貿易便 捷化及貿易與創新政策原則,以及MCO/MCP 與ITA擴大談判議題進行研商。會中我國針對 WSC提出之貿易便捷化原則率先發言表示,鑒 於貿易便捷化為WTO杜哈回合談判小型套案之 重要議題,GAMS成員應共同對WTO年底部長 會議就該議題達成具體成果宣示支持,以回應 產業界之期待,並獲其他GAMS成員之支持, 會議決議GAMS支持WTO於本年完成貿易便捷 化協定談判,並將責成其談判人員推動將WSC 貿易便捷化原則納入談判成果。

另GAMS亦於本次會議具體回應WSC之 建議,同意配合下次GAMS會議時程,針對加 密議題召開政府官員與專家會議討論,以利 將加密原則落實為更具體的行動。同時由於 GAMS成員均認為會議召開前應有更具體的規 劃,因此將與WSC進一步研商。至於WSC希 望GAMS支持之貿易與創新政策原則,雖該原 則主要內容均源自APEC創新政策領袖聲明, 惟因歐盟表示其非APEC會員體,需要更多時 間就該等原則進行檢視,雖討論過程中美方曾 主張GAMS應對該等原則表達更強烈的支持之 意,最後會議決議仍僅就WSC提出該等原則表 示歡迎。

關於MCO與ITA擴大談判,由於中國大陸 對於MCO定義維持原立場,並主張該定義及目 前的ITA擴大談判清單均有「泛IT化」的問題, 因此,本次會議對於推動支持MCO定義納入 HS2017版內容及ITA擴大談判清單並達成具體 成果等產業界建言,仍僅有中國大陸以外其他5 個成員達成共識。另觀察本次會議中國大陸出 席代表雖發言態勢較為和緩,但立場仍相當堅 定,會中中方並明確表示,中國大陸在低階IT 產業面臨產能過剩問題,故目前符合MCO定義 範圍之產品將觸及中方敏感產業。

#### (三)共同保護全球環境

本議題由於WSC關切美國加州擬訂之加 強消費者安全法案之實施恐造成貿易障礙,爰 美方於會中進一步說明已就該法案進行WTO 通知,並已多次舉辦公聽會徵詢各界提出評論 意見。會中我國與歐盟均強調法規調和之重要 性,並重申應將WSC之建議納入考量。各會員 對於美國前揭法案均未提出關切事項。

#### (四)衝突礦石

除歐盟針對衝突礦石分享其依據OECD指 導原則訂定之相關規範外,GAMS亦同意將致 力於推動採行全球性及產業導向之法案,以辨 識無衝突的冶煉廠。

#### (五)區域振興經濟

本議題雖美國與歐盟產業界原擬議之溝通 機制經過1年的討論仍未能於WSC達成共識, 惟歐盟及美國仍希望GAMS能請WSC持續討 論,但日本、韓國及我方均認為此議題已討論 多年,爰主張應在WSC就相關建議達成具體共 識後再送交GAMS進一步考量。最後,在各成 員的妥協下,同意邀請WSC就達成的具體進展 向GAMS提出報告。

### 2013年9月韓國濟洲島 JSTC會議記要

陳淑芬協理/TSIA

2013年GAMS會議於9月26日假韓國濟州島Lotte Hotel舉行,由韓國政府主持,與會者包括來自台灣、中國、日本、韓國、歐盟、及美國之政府代表。台灣GAMS代表團由國貿局江文若副局長率4位政府代表與會。 JSTC及其他專案小組會議則於23-27日於同一地點召開,主辦單位為韓國半導體產業協會(KSIA),包括台灣、日本、歐盟、中國、及美國的半導體協會均派代表出席。台灣半導體產業協會(TSIA)由台積電王一飛資深處長 (本會JSTC主席)率團,成員包括瑞昱半導體黃依瑋副總(本會JSTC共同主席暨IP工作小組召集人)、台積電劉 彥顯資深律師、台積電許芳銘處長(ESH)、法律顧問Christopher Corr、秘書處陳淑芬協理及石英堂資深經理。

#### 相關討論及決議摘要如下:

- 1.產業成長議題(Growth Initiative): 此議題由本會盧超群理事長於2013年5月WSC會議中首度提出,並經與會各國CEO同意, JSTC正式成立工作小組, 由美國半導體協會(SIA)出任工作小組主席, 並由本會擔任副主席, 共同推動此議題的討論。此次工作小組會議於9月23日召開, 本會由台積電王一飛資深處長、法律顧問Chris Corr、及陳淑芬協理代表參加。會中針對本會與SIA共同研擬之草案進行討論, 相關結論包括:

- a.縮小討論範疇,只集中在WSC較適合討論的事項。

- b.在如何成長產業方面主要分三個方向,由各負責協會研究在各自地區有利於產業發展或阻礙產業成長之相關規定,於下次會議中報告並提出建議。三個方向如下:1) Energy Efficiency:由本會及日本半導體協會(JSIA)共同負責;2) Automobiles:由歐盟(ESIA)及美國(SIA)半導體協會負責;3) Healthcare:由韓國(KSIA)及中國(CSIA)半導體協會負責。惟ESIA表示無法在現場承諾,JSTC會議中決議ESIA於10/15前確認其是否同意接受此提案。

- c.在吸引人才部份:JSTC決議在WSC聯合聲明中,新加入一段"Attracting Talent to the S/C Industry",並由本會草擬相關文字。各協會並同意於12月中以前分享各地區吸引頂尖人才之做法。

- d.在研發挑戰部份:JSTC同意ITRS的要求,在 2014年5月WSC會中安排ITRS進行技術相關報告,由SIA負責與ITRS聯繫。各協會也同意在 2014年1月中以前分享各自政府對半導體產業相 關的技術及科學方面之政策內容。

瑞昱黃依瑋副總經理主持WSC IP 委員會會議

- 2. 推動MCO產品零關稅之進展:工作小組會議於9 月24日召開,並針對ITA談判停滯一案對JSTC提 出報告。由於此議題已討論多年(自2006年始), WSC及GAMS成員多有共識欲儘速達成協議。

- a. 擴大ITA談判目前處於停滯狀態, JSTC決議邀請全球半導體CEO聯合署名,於10月初致函中國政府高層表達全球半導體業界之期望。

- b. 對於MCO產品納入世界關務組織(WCO) HS2017 review一案,美國政府已將產業之 MCO定義送交WCO,後續工作如下:1)各協會將持續提供各自政府在技術上之諮詢;2) SIA將於10月中將WCO-HSC 9月比利時會議之結果與各協會分享;3)各協會分別於10月及12月洽詢各自政府代表了解擴大ITA談判之進展,並向ESIA回報;4) MCO工作小組於12月WTO部長級會議後召開電話會議討論ITA及MCO進展及後續計劃。

- 3. 反仿冒工作小組:反仿冒會議於9月23日下午召開,並對JSTC提出四項建議,包括:a) 各協會研究於各協會中成立"Awareness campaign"之可能性;b) 各協會研究於各自協會中成立反仿冒工

作小組之可能性;c)各協會鼓勵會員向海關註冊 "Application for Action";d)各協會應正視仿冒問題的嚴重性。針對以上建議,各協會同意在收到 ESIA進一步草擬的表格後,分享實行計劃;針對 SIA的反仿冒立場白皮書,各協會同意於11月底前回覆是否同意背書;對於JSIA所印製之反仿冒宣導海報,各協會將回報未來一年內適合張貼此海報之場所及活動。

- 4. IP Committee: IP委員會會議於9月24日召開,本會自此次會議開始擔任輪值主席,由瑞昱黃依 瑋副總代表本會接任。相關重點如下:

- a. 營業秘密:各協會於12月中以前,針對SIA 之提案提出意見,尤其在各國營業秘密保護 法之最佳範例、公司內部配合法規之相關措施、及TRIPS相關規定之不足等,同時也 分享對於KSIA所分享之韓國original trade secret certification之看法。委員會成員也歡 迎進一步分享如何處理新運算技術(例如雲端 技術)所衍生的營業秘密保護之挑戰。本會身 為委員會主席,需負責草擬明年WSC聯合聲 明之相關文字。

- b. NPE/PAE: SIA分享了美國政府相關單位與此議題有關之研究及進展,也說明了SIA對此議題的立場由原先的不方便談轉變為著重在"abusive patent litigation",JSTC支持SIA於8月1日發表關於此議題的立場白皮書,各協會同意向各自政府表達業界支持美國政府針對abusive patent litigation的相關立法。至於WSC是否該積極參與FTC Sec. 6(b)的調查,各協會間並未達成共識。

- c. Utility Model Patent(新型專利): IP委員會提出

一份調和Utility Model Law之建議,此份文件就

申請內容、可專利性、執法面、及與專利間的

關係等事項提出建議,並於JSTC會議中獲得共

識。各協會同意於會後徵詢各自CEO之意見,

並於獲得CEO同意後,由委員會主席以此文件

向世界專利組織(WIPO)正式提出建議。

- d. Patent Quality: WSC已向WIPO提出由WIPO 統一收集各國有關改善專利品質之相關數據, WIPO並建議WSC協會向各自政府尋求支持。 目前CSIA及ESIA尚未得到政府的回應。CSIA 與ESIA同意於2014年1月中之前分享其專利局 之立場。

- e. Patent Harmonization: SIA提出一份有關專利調和之建議,內容包括prior user right, first-to-file grace period, conflicting applications, 及publications,各協會同意於1月中以前分享對SIA建議的看法。

- f. WIPO視訊會議:IP委員會與WIPO的視訊會 議於9月25日JSTC會後舉行,WIPO代表為 Deputy DG James Pooley及Matthew Bryan, Director, Patent Cooperation Treaty Legal Division。James Pooley說明了WIPO在專利品 質、新型專利、營業秘密保護、及專利濫訴等

- 議題的做法, WSC IP委員會亦說明了委員會目前討論的重點。雙方都認為這樣的視訊會議很有意義, 也同意未來可以增加雙方視訊會議的頻率。

- 5. Encryption: 5月里斯本會議雖通過要針對各國加密產品認證規定及認證現況進行survey,但由於有些協會不確定survey內容,有些協會表示survey要求項目屬機密,因而無法取得資料,以致於由ESIA主導的survey未能完成,這使得ESIA有些挫折,並於幾天的會議期間分別與各協會進一步會談,期能解答各協會的疑惑並尋求大家的支持。會後各協會同意進一步研究如何完成survey回報給ESIA匯整。

- 6. Export and/or Import Regulatory Restrictions:本會於9月24日召開的工作小組會議中針對歐美等國之出口管制作業提出建議,SIA對其中基礎研發因出口管制所遭遇到之困境十分認同,因而對本會之相關建議表示支持,各協會同意在下次會議之前討論本會所提之建議,包括申請程序透明化,加開海外說明會等。

- 7. 環安衛:委員會會議於9月23-25日召開,由本會環安衛委員會主任委員許芳銘(台積電處長)帶團,成員包括台積電羅明廉副理、聯電賴懷仁副處長、工研院呂慶慧資深研究員、及本會秘書處石英堂資深經理。會議結論包括:

- a. PFC: 2013資料需於2014年3月底前交給委員會主席匯整;研議IPCC guidelines的更新程序;分享HCFC/HFC substitution計劃;持續定期檢視最佳範例及觀察技術演進等。

- b. Resource Conservation:此工作小組由本會代表台積電許芳銘處長擔任主席,會中決議包括:各協會同意檢視節能評估方法的兩項提案;尋求與供應商共同推動resource conservation之策略等。

- c. Chemical:工作小組關切中之議題包括

Nanomaterial Project及韓國REACH之立法

等,工作小組決議將致函韓國政府表達業界對

其REACH立法之疑慮。

- 詳細ESH委員會討論內容,請參閱下一頁WSC環 安小組會議記要。

- 8. 振興經濟方案: SIA與ESIA持續推動此議題,但並未有新的進展。

- 9. 衝突礦石(Conflict Minerals): 美國SEC(the Securities and Exchange Commission)在2012年8月22日通過此立法,並於8月23日公佈,業界持續在評估該立法的衝擊。在此立法下,公司必需揭露其所使用的來自剛果共和國的礦石材料(即衝突礦石)。WSC已於2013年5月通過無衝突供應鏈立場白皮書。下次會議中,SIA將分享EICC/GESI程序,也將邀請非半導體廠之EICC會員分享。各協會也將對會員公司目前處理狀況進行調查。

- 10. **WSC2.0**: WSC2.0工作小組會議於9月26日下午召開,會中達成多項決議,重點如下:

- a.有協會提議延長GAMS會議,讓政府代表有較多討論時間。JSTC認為需由GAMS決定是否延長,各協會同意徵詢各自政府意見。本會已徵詢台灣GAMS代表之立場,並獲得台灣GAMS之正面回應。JSIA身為明年GAMS/JSTC主辦協會,將草擬詳細的會議時間表提供討論。

- b.由於討論議題眾多,明年二月將召開WSC2.0工作小組特別會議(原訂一年只召開一次會議)。

- 11. Membership: JSTC討論SIA草擬之"觀察員"會 員身份之權利義務,但未獲得共識。本會提出一 些問題供大家思考,各協會同意進一步討論後於 11月中回覆意見。下次會議仍將與此次會議一 樣,邀請新加坡半導體協會(SSIA)以guest身份 與會。

- 12.未來會議: 2014年2月之JSTC會議將由JSIA主辦,地點在日本神戶; 2014年5月之WSC/JSTC會議由本會(TSIA)主辦,地點在台北; 2014年9月之GAMS/JSTC會議由JSIA主辦,地點在日本福岡。

本會現已出任WSC環安衛委員會Resource Conservation工作小組及WSC IP委員會主席,加上因主辦明年WSC CEO年會而將再接下WSC Market 委員會及WSC 2.0工作小組主席,希望透過與會團隊的努力,加強TSIA在這個代表全球半導體產業的重要國際場域之參與度;也借由台灣代表們的優異表現,提升台灣半導體產業的形象及台灣在國際的能見度。期盼會員持續支持並踴躍參與本會的各項討論,若對各項議題有疑問或建議,歡迎與TSIA秘書處聯絡。

## 2013第二次 WSC 環安小組

會議記要

呂慶慧資深研究員/工研院

#### 一、會議背景

2013年世界半導體協會第二次安全衛生功能 小組(WSC ESH Committee)會議,於2013年9 月23日至2013年9月25日在韓國濟洲島舉行。 本次會議主要分為三個主題進行討論,分別為: PFC, Chemical及Resorce Conservation。在會 中TSIA代表提出國內半導體產業的意見與建議, 並積極為國內產業蒐集資訊及爭取權益。本次環 境安全衛生功能小組會議,是由環安委員會許芳 銘主委領隊,台積電羅明廉副理負責PFC工作小 組、聯華電子賴懷仁副處長負責Chemical工作小 組、許芳銘主委及工研院呂慶慧資深研究員負責 Resorce Conservation工作小組。

#### 二、區域性的法規更新

本次在各國法規更新方面,以歐盟之含氟溫室 氣體管制檢討、美國環保署法令及奈米顆粒法規更 新最多,茲分別說明如下;

#### 1.歐盟法規更新

氟化氣體佔歐盟2010年所有溫室氣體排放約 2%(CO2當量),且此比例仍持續增加中。當其 他主要類別的溫室氣體排放在1990至2011年間 顯著減少,氟化氣體排放卻增加了50%(CO。當 量)。氟化氣體主要有氫氟碳化物(HFCs)、全氟 化碳(PFCs)與六氟化硫(SF<sub>6</sub>)三類,一噸SF<sub>6</sub>相當 於24000噸二氧化碳的全球暖化力。歐委會2012 年提出新氟化氣體法案,企圖在2030年前減少目 前氟化氣體量2/3,此提案仍在歐議會及歐洲理 事會討論中。而在現行氟化氣體法規下,會員國 必須改善含氟化氣體設備的滲漏緊度,且若有較 有益環境的其他選擇,則應避免使用這些設備。 牛產、進口或出口超過一噸氟化氣體的公司須向 歐委會申報數量,歐洲環境署發表的「氟化溫室 氣體2012」公布129家公司所申報的總量。此報 告指出,以二氧化碳當量計算時,過去兩年的出 □量是自2007年開始申報以來最高的。而歐盟氟 化氣體供應淨量,使用於製冷與空調的HFCs佔 62%,使用於製造電氣設備中的SF。則佔23%。 未來歐盟將以2008年至2011年的使用量做為未來 核配的基礎。

#### 2.美國Reporting Rule

本次SIA仍以Reporting rule進度為報告主軸。 未來PFCs可能取消以製程化學品使用條件進行申 報方式,而以更細的蝕刻分類或管末監測為申報 的基準。2011年起,美國環保局強制要求國內28 個產業部門,在9月底前,利用此線上系統遞交各 部門2010年相關之溫室氣體盤查報告,並規劃彙 整這些匯報資料,完成國內產業部門之溫室氣體 資料庫建置。目前已經有超過1000名行業協會、 政府與非政府組織對此系統進行測試,並保證這 項工具對於溫室氣體計算方法的公正性以及友善 的操作介面。另外,有關氦氣的使用方面,在美

國聯邦法令規定在2013年前70%氦氣歸國內使 用,30%供應給全球使用,以穩定需要使用氦的 國家。

#### 3.KSIA在本次法規分享了K-REACH法規

繼日本與中國大陸受歐盟REACH法規影響 後,相繼參採歐盟REACH精神完成該國化 學品管理法規修訂,韓國環境部於日前公告 「化學物質註冊評估法」初稿(Act concerning Registration, Evaluation, etc. of Chemical Substances), 或稱為Korea REACH, 已於2013 年3月9日正式向世界貿易組織(WTO)通報預告立 法,國際間廠商們耳聞韓國版REACH法規的草 擬已久,也呼應了年初韓國所提出的跨部會國家 2020年化學物質管理策略方案中有關環境部的具 體行動,本法規預定於公告後兩年內正式實施(預 計2013或2014年間)。韓國環境部公告的新草案 將全面修訂以取代原毒性化學物質管理法,主要 加入歐盟REACH法規的相關管理元素與作法, 該法規類似歐盟REACH法規要求預註冊、唯一 代表人、順數級距的資料需求等。依KSIA分享之 資料顯示,在2015年前,使用量大於100噸之新 化學品,皆需要準備化學安全性報告(CSR),以 後逐年會修定申報門檻,預期在2020年前將減至 10 順以上者皆需要準備化學安全性報告(CSR)進 行註冊申請。預期韓國版REAHCH作法將與歐盟 REACH法規有諸多雷同作法。

#### 三、在各小組的討論結果方面分述如下:

#### 1.在PFCs方面;

本次主要是討論資料的蒐集並回覆GAMS問 題。上次GAMS是強調目標是以Normalize,透 明度(包含使用量)及第三者認證問題。本次會議 各協會依各國政府要求進行申報,並不需要強 制性的第三者查證工作。但在Best Practice方 面,TSIA提出希望能有較合適的香核或追蹤程 序,了解各協會因應的技術發展,TSIA將在下 一次會議提出查核構想。另外有關韓國提議將 集中式的管末處理機制列入Best Practice範圍, 因此技術有許多不確定資訊,委員會希望韓國 能提供更多的資訊。本次會議亦提及HFCs及 HCFCs未來管制的趨勢與想法,但此議題屬國 家層級的範圍,各協會認為應配合國家的法規 進行管理排放。

#### 2.在化學品小組方面;

本次討論的議題包含Korea-REACH, California Green Chemistry, US-EPA Toxic substances control act (TSCA), Chinese Taipei-REACH, EU REACH-nMP, PFOA/PFOS, Nanomaterials發 展。其中以Korea-REACH討論最多。另外有關 REACH-nMP未來有可能管制/限制進口,國內廠 商需要嚴密監控因應。

#### 3.在Resorce Conservation工作小組方面;

去年ESH Committee決議未來不再規劃2020 年的能源目標, 並基於整體資源的使用, 將 Energy Saving改為Resource Conservation, 以擴大整體半導體業對社會環境責任的貢獻分 析。本次TSIA提出的節能展現方法學,言簡精要 各國並無多大意見。各協會同意回去研究了解並 於11月15日前提供意見給TSIA,並於11月30日 前召開電話會討論。

15■ 台灣半導體產業協會簡訊 NO.66 October ■

# **GLOBAL VIEW**

### **JEDEC Mobile Forum Taiwan** 2013活動報導

吳素敏資深經理/TSIA

3年JEDEC行動裝置高峰論壇(JEDEC Mobile Forum)分別於5月中旬、8月13日、15日,於美國Santa Clara、韓國首爾及台灣新竹舉行。

今年Mobile Forum Taiwan仍由JEDEC固態技術協會與IDB(工業局)、ITRI(工研院)、TSIA(台灣半導體產業 協會)於2013年8月15日(四)假新竹市國賓大飯店聯合舉辦,提供台灣業界最新行動裝置記憶體相關技術標準, 及對現在與未來相關應用的影響與對應策略。

本次論壇活動焦點是以最新行動裝置記憶體技術及相關標準為主軸,內容涵蓋: Memory & Roadmap, Mobile & Speed need, Compute Device, UFS, UFS & e.MMC, LPDDR3/4, and Storage Solutions 等,邀請來自全球的領導廠商蒞會分享,包括Samsung, Qualcomm, ARM, Micron, Toshiba, Synopsys, Arasan, Agilent等大廠蒞會演講JEDEC最新標準成果。

本次共吸引約400多人報名,約300人與會,與會來 賓皆是記憶體相關廠商,首先感謝經濟部工業局(IDB)、 工研院(ITRI)協助辦理本活動,更感謝聯華電子金級贊 助、南亞科技及鈺創科技銀級贊助,及其他參加廠商的 參與支持,包括A-DATA(威剛科技)、Advantest(愛德萬 測試)、Allion Labs(百佳泰)、AP Memory(愛普科技)、 Arasan Chip Systems、Argosy(優群科技)、ASE(日月 光半導體)、ASolid(點序科技)、ATP(華騰國際科技)、 Avery Design(亞睿資訊)、Cisco Systems(台灣思科系 統)、Copystar(安辰電腦)、ECLTB(荷蘭商伊士曼化工)、 Elpida Memory、eMemory(力旺電子)、Enthone(美商樂思 化學)、ESMT(晶豪科)、Etron(鈺創科技)、Fairchild(美商 快捷半導體)、Faraday(智原科技)、Genesys Logic(創惟科 技)、Greenliant、GUC(創意電子)、Hermes(漢民科技)、 Hewlett Packard(HP)、Horizont(和豐國際)、Huawei(訊崴 技術)、Innostor(銀燦科技)、Innotest(環國科技)、Intel、 ISSI(砂成積體電路)、IST(宜特科技)、ITRI(工研院)、 Kingmax Digital、Kingston(遠東金士頓)、Lite-On IT(建 興電子科技)、Marvell(邁威爾科技)、MediaTek(聯發科)、 Memoright(憶正科技)、Micron Technology(美光科技)、 MPI(旺矽科技)、MXIC(旺宏電子)、NITTO DENKO(台灣 □東電工)、NTC(南亞科技)、NTK(聯詠科技)、Nvidia、 Phison(群聯電子)、Powerchip(力晶科技)、PTI(力成科 技)、ROHM(羅姆半導體)、Samsung(三星電子)、Sensata Technologies、Silicon Motion(慧榮科技)、SK Hynix(海 力士)、SkyMedi(擎泰科技)、Solid State System(鑫創科 技)、SPIL(砂品精密工業)、Spirox(蔚華科技)、Storart Technology、Sunplus(凌陽科技)、Synopsys(台灣新思科 技)、TE Connectivity (百慕達泰科電子)、Tmtech(凱鈺科 技)、Transcend(創見資訊)、TSMC(台積電)、UMC(聯華電 子)、Walton(華東科技)、Winbond(華邦電子)、Wintec(兆創 科技)等60幾家海內外手持裝置相關公司與會,是台灣與全 球手持裝置專家交流之絕佳機會及平台。

#### **Morning Session Keynote & Speakers**

Keynote DY Lee, Samsung

Rick Wietfeldt, Qualcomm

Ivan Lin, ARM

Dan Skinner, Micron

17■ 台灣半導體產業協會簡訊 NO.66 October ■

瞭望

Opening Mian Quddus, JEDEC BOD Chair

Morning Session Moderator Henry Lee, Sunplus

**Afternoon Session** Moderator TC Hsiao, ESMT

#### **Afternoon Session Speakers**

Toshio Fujisawa, Toshiba

Venkataraghavan PK, Synopsys

HeeChang Cho, Samsung

Sam Sungmin Park SK, Hynix

Hung Vuong, Qualcomm

Joe Mallett, Arasan Chip Systems

Perry Keller, Agilent

午餐聯誼會

大會由TSIA「消費性電子記憶體介面標 準推動小組(Consumer Electronics Memory Interface Forum)」現任召集人凌陽科技李桓瑞 特助及新任副召集人晶豪科技蕭子哲處長主持, JEDEC主席Mian Quddus蒞臨開幕。本次活動感 謝TSIA「消費性電子記憶體介面標準推動小組」 召集人、副召集人暨推動小組全體成員全力支 援,及感謝所有合辦單位、參與業界公司及工作 人員的全力協助,讓本次活動圓滿成功。

JEDEC JC-16,40,42,45,63,64小組的國際標準 制定會議,2013年第四次標準制定會議將於12月 9-13日假美國夏威夷茂宜島舉行,歡迎JEDEC會員 公司派員參加。若您對JEDEC會議有興趣,但尚不 是JEDEC會員,歡迎與台灣半導體產業協會聯繫, 請聯絡TSIA吳素敏資深經理(Tel: 03-591-3477; Email: julie@tsia.org.tw)或TSIA消費性電子記憶體 介面標準推動小組(Consumer Electronics Memory Interface Forum)新上任召集人聯發科宣敬業經理 (Email: jy.shiuan@mediatek.com)

### JEDEC 2013 Q3 美國奧斯汀

### 會議報告

宣敬業經理/聯發科技 邱濱棋經理/華邦電子

#### 壹、前言:

JEDEC(聯合電子裝置工程協會)於2013 年9月9日至13日在美國奧斯汀召開記憶體 規格制定研討會議,共有一百五十五位, 來自全球六十七家廠商之代表參與。本次 會議之議題包含動態記憶體(DRAM)規格、 非揮發性記憶體(Non-Volatile Memories) 規格、低功率記憶體(Low Power Memory) 規格、動態記憶體模組(Memory Modules) 規格、快閃記憶體模組(Flash Modules)規 格、多重晶片封裝(Multichip Assemblies) 規格、邏輯電路規格及介面電氣規格。其中 在LPDDR4、WideIO2、eMMC及UFS等 各項記憶體規格標準之制定,各相關委員會 通過大部份之規格票決案。

JEDEC會議台灣代表廠商

| 委員會    | 規格                                  | 委員會    | 規格                                                      |

|--------|-------------------------------------|--------|---------------------------------------------------------|

| JC42   | Memory                              | JC16   | Interface Technology                                    |

| JC423B | DRAM Functions, Features & Pinouts  | JC40   | Digital Logic                                           |

| JC423C | DRAM Timing and<br>Parametrics      | JC40.4 | Registered & Fully Buffered Memory Module Support Logic |

| JC424  | NonVolatile Memory (Flash etc.)     | JC40.5 | Logic Validation and Verification                       |

| JC426  | Low Power Memory                    | JC63   | Multiple Chip Packages                                  |

| JC45   | Memory Cards and Modules            | JC64   | Flash – Embedded, Cards and Modules                     |

| JC45.1 | Registered Modules (RDIMM)          | JC641  | Electrical Specifications                               |

| JC45.3 | UDIMM, SODIMM, MiniDIMM, etc.       | JC642  | Mechanical Specifications                               |

| JC45.4 | FBDIMM, LRDIMM, etc.                | JC645  | UFS Measurement                                         |

| JC45.5 | Connector Electrical Specifications | JC648  | Solid State Drives (SSD)                                |

| JC45.6 | Hybrid Modules                      | JC649  | Wireless Memory                                         |

21■ 台灣半導體產業協會簡訊 NO.66 October ■ ■ 台灣半導體產業協會簡訊 NO.66 October ■22

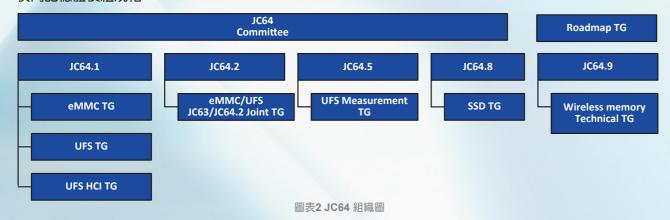

### 参、本會期之重要議題或技術趨勢摘要:

#### 非揮發性記憶體規格:

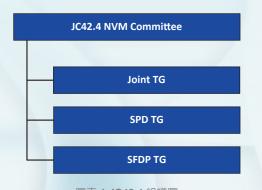

圖表 1 JC42.4 組織圖

JC42.4是非揮發性記憶體規格委員會,此次主要議題是Toggle NAND Flash3.0的資料更新。

#### Toggle DDR 3.0 target

- SSD and mobile storage speed is going faster

- To support  $\underline{\sf eMMC}$  5.5,  $\underline{\sf UFS}$  2.0, and  $\underline{\sf PCIe}$   $\underline{\sf Gen3}/4,\ \underline{\sf NAND}$  interface speed should be faster than now

- Toggle  $\underline{DDR}$  3.0 targets up to  $\underline{800Mbps},$  which is double of precedent Toggle  $\underline{DDR}$  2.0

- Power is more important on high speed

- As data transfer speed increases, power consumption concerns is becoming more significant

- Toggle  $\underline{\text{DDR}}$  3.0 spec defines not only  $\underline{\text{1.8V}}$  but  $\underline{\text{1.2V}}$  for IO voltage

其中Toggle DDR 3.0較著重在下列幾點

- Supporting V<sub>CCQ</sub>= 1.2V & 1.8V

- · DC/AC spec

- 1.1.14~1.26V

- 2.VIH(DC)min= VREFQ+100, VIH(DC)max=  $V_{CCQ}$

- 3.VIH(AC)min= VREFQ+150, VIH(DC)max= Overshoot spec

- 4.VIL(DC)min= V<sub>SSQ</sub>, VIL(DC)max= VREFQ-100

- 5.VIL(AC)min= Undershoot spec, VIL(AC)max= VREFQ-150

- ZQ Calibration

- 1.Opcode: JTG agree to assign F9h & D9h for ZQ calibration

- 2.RZQ pin location for BGA-132/152: K4 & H10

- 3.RZQ pin location for BGA-272/316 : same location as defined

- 4.ZQ resistor value: 300ohms

- 5.Status Read during ZQ calibration busy period : Status Read operation shall not be performed during the period and R/Bn pin shall be used

- 6.RTT value: he device supports 50, 75, 100 & 150 ohms.

#### 快閃記憶體模組規格:

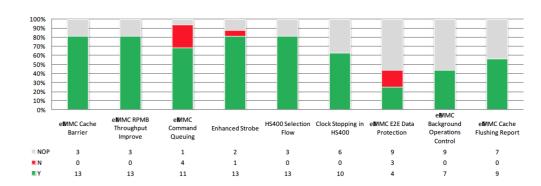

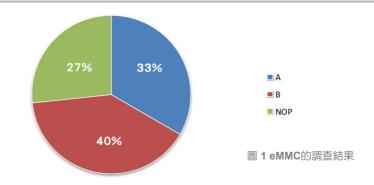

未來路線小組完成了eMMC及UFS的調查,大部分的公司依然希望在eMMC及UFS的領域能有持續性的更新。

• Q-A1: Does your Company agree to include the features listed below in the next spec revision(s)?

但在完成這一次的eMMC規格的更新後將不會有新一代的規格進版

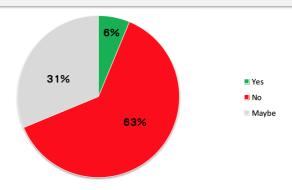

• Q-A2: Does your Company plan to propose additional features on top of the ones mentioned in the list in Q-A1 for the next eMMC Standard?

對於Command Queuing的議題,大部分的公司仍然支持這個方案

- Q-A3: Command Queuing. Please provide an opinion on the following options:

- Option A. If you Company plans to support Command Queuing, does it prefer Command Queue with changes at interface & adding an additional pin?

- Option B. If your Company plans to support Command Queuing, does it prefer Command Queue with only controller changes (host and device) & protocol changes but no changes on the interface?

**GLOBAL VIEW**

在2013年9月公布eMMC5.0規格之後。eMMC 5.x的更新持續的討論,主要提供了下列新的功能。

- eMMC Background Operations Control

- eMMC Cache Flushing Report

- · Cache Barrier

- eMMC RPMB Throughput Improve

- Enhance strobe for HS400

- · eMMC command queue pin

- · eMMC command queuing

- HS400 Clock Stopping Clarification

- eMMC Command Queuing Host Controller Interface

在2013年9月公布UFS2.0規格之後。UFS2.x的

更新持續的討論,主要提供了下列新的功能。

- · New voltage

- · FFU timeout Descriptor

- · Device Health Descriptor

- Handling RTT Race Conditions

- · UFS Command Priority

- · UFS Device Assistance for Encryption by Host

- UFS FFU

- · Production state awareness

- PWM Reference Clock Clarification

- · UFS Unified Memory Extension Update

- Clarification of bLUQueueDepth

- More Flexible Slew Rate Control

- UFS I/O Virtualization

- 1. Architecture Overview

- 2. Multi-Initiator Support in a UFS device

- 3. UFS Partition Table Descriptor

- Updated RPMB frame size

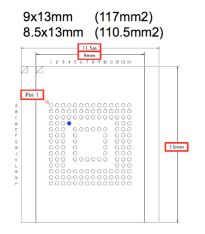

在eMMC的封裝包裝提案上,因為不同公司的晶 片形狀不一,所以這次有兩個不同的提案,但是不 少公司反映這樣不會有好處,並且希望能夠有一個 融合方案。

#### 動態記憶體規格:

#### HBM(high bandwidth memory)動態記憶體:

HBM完整規格0.97版在2013Q1會議中已完成 委員會投票通過,0.99版仍待委員會投票決定。 本期會議中,新的規格提案包括Pseudo channel addressing, Micro bump field area proposal及 Implicit Precharge.

#### DDR4動態記憶體:

DDR4-2133規格已於2012Q3公告, DDR4-2400規格於2013Q1通過BOD審查。本期會議中, 新的規格提案包括DDR4-2666, DDR4-3200時序規 格以及Post Package Repair功能之進一步修訂。

#### GDDR5動態記憶體:

GDDR5規格已於2012Q2公告,本期會議中未 有GDDR系列的新的規格提案。

#### 低功率記憶體規格:

#### LPDDR3低功率動態記憶體:

LPDDR3進階版本LPDDR3-1866及 LPDDR3-2133已於2013Q2會議中通過提交BOD審 查並於9月3日公告。本期會議中未有LPDDR3系列 的新的規格提案。

#### LPDDR4低功率動態記憶體:

LPDDR4規格制訂,本會期共有53案通過委員 會之票決以及15件新的規格提案,完整規格書初稿 預計於2013年Q4提交委員會票決,預計在2014年 Q1公告第一版規格書。

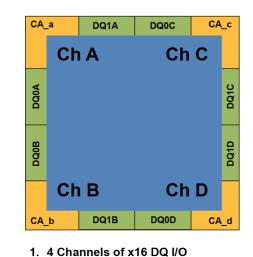

LPDDR4規格的主要特徵包括下列各項:

- 16 Data Bits per channel

- 4200Mbps per bit data rate

- · 16.8GB/s with two 16b channels

- · No PLL or DLL in the DRAM

- · Support for Post Package Repair

- VDDQ = VDD2 = 1.1V

- VDD1 = 1.8V

本會期中已有三件新的提案提出LPDDR4的封裝 規格,其中一案既由聯發科技提出,會中委員會決 議封裝規格應從應用需求之觀點整體考慮,責成工 作小組再行研議。

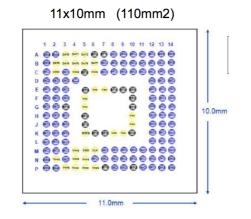

#### Wide IO 2低功率動態記憶體:

WIO-2規格制訂,本會期共有17案通過委員會 之票決以及4件新的規格提案,完整規格書初稿亦於 本會期發表,預計於2013年Q4提交委員會票決,預 計在2014年Q1公告第一版規格書。

WIO-2規格的主要特徵包括下列各項:

- · 64 Data Bits per channel

- · 25.6GB/s and 34.1GB/s with four 64b channels (4x64 die)

- 51.2GB/s and 68.3GB/s with eight 64b channels (8x64 die)

- · Configurable with1, 2, or 4 stacked die for bandwidth and capacity scaling

- Unterminated CMOS I/O signaling

- No PLL or DLL in the DRAM

- Multiplexed Command Address (11 CA signals over 2 UI)

- Support for supplier specific Direct Access Mode test feature

- · Support for GPIO Mode test access

- · Support for Post Package Repair

- VDDQ = VDD2 = 1.1V

- VDD1 = 1.8V

#### 多重晶片封裝(MCP)規格:

此次會議中,LPDDR4的封裝,在POP封裝包 裝提案上,因為在會前的討論時已經達成一定的共 識,所以這個提案順利的進入下一輪的表決,但是 在分離式的封裝包裝討論上有三家公司各自提出提 案,所以仍需要更進一步的討論。

Different Suppliers have Different Die Aspect Ratio (Square & Rectangular) Different die sizes at every supplier, density, and lithography Common Small size should be supported by both types of die designs

Committee should agree on one smaller size that ALL NAND Suppliers can support to best service the industry

# 272ball POP ballout proposal Note 1: 15x15 mm, 0.4mm pitch, 36 rows

- 1. Package dimension: 15 x 15 mm<sup>2</sup>, 0.4mm pitch

- 2. Ball count: 272 balls

- 2. CA on all four corners

- 3. 4 ZQ pins

- 4. 1 RESET n pin

**B** 9 LPDDR4 POP package

#### 肆、結論:

在快閃記憶體模組領域,eMMC5.0及 UFS2.0的規格已在2013年9月公布。未 來將會討論下世代eMMC及UFS的發展方 向。尤其eMMC将在下一次的規格公布之 後就不再更新,所以這次的討論將會是最 終版的討論。

在動態記憶體領域,DDR3及LPDDR3 規格已制定完整, DDR4, LPDDR4, WIO2,及HMB亦將於近期制定完成並完 成公告。

JEDEC董事會於本次會議中亦呼籲會 員及企業積極參與JEDEC,並針對未來新 一代記憶體的走向及發展希望會員能夠更 積極及深入的討論。

#### 伍、後記:

JEDEC JC-16 , JC-40 , JC-42 , JC-45, JC-63及JC-64小組的國際標準制定 會議,2013年第四次標準制定會議將於 2013年12月9日至13日假美國夏威夷舉 行,歡迎JEDEC會員公司派員參加;同時 這也是一個絕佳的國際交流平台,歡迎相 關單位及廠商贊助,贊助細節請洽台灣半 導體產業協會(TSIA)。若您對JEDEC會議 有興趣,但尚不是JEDEC會員,歡迎與 TSIA聯繫,請聯絡TSIA吳素敏資深經理 (Tel: 03-591-3477; Email: julie@tsia. org.tw)或TSIA消費性電子記憶體介面標準 推動小組(Consumer Electronics Memory Interface Forum)召集人聯發科技宣敬業 (Email: jy.shiuan@mediatek.com) •

### **Joint Symposium 2013** e-Manufacturing & Design **Collaboration Symposium and** ISSM 活動報導

石英堂資深經理/TSIA

\_本會主辦之Joint Symposium 2013 -中曾王斯定00mm e-Manufacturing Design Collaboration Symposium and ISSM 於9月6日假新竹國賓大 飯店舉辦。本研討會今年再次與半導體產業之 指標研討會ISSM(International Symposium on Semiconductor Manufacturing)共同舉辦。會中特別 邀請工研院IEK蘇孟宗主任擔任Keynote Speaker, 講題為Next Step for Taiwan Memory Industry, 同時邀請Mentor Graphics之Foundry Programs Director – Ms. Shu-Wen Chang進行演講。

因BigData Solution之應用越來越顯重要 特別辦理"BigData Solution Applications for Semiconductor Industry"專題,集結EMC<sup>2</sup>、Intel BISTel \ IBM \ Microsoft \ PDF Solutions \ SAS SAP、Trend等指標廠商發表最新技術進展與應用。 除了特別邀請的演講外,本次研討會同時由國內外 產學界發表35篇論文。研討會內容充實並涵蓋目前 重要之生產議題,與會者皆感不虛此行。本研討會 共計260人參與。本次活動特別感謝Intel、EMC $^2$ 、 Anchor BISTel BM Mentor Graphics Microsoft > PDF Soultions > SAP > SAS > Trend的 熱情贊助。

### TSIA理監事會推動產業發展研討會

### 活動花絮報導

黃佳淑經理彙整/TSIA

#### 有關TSIA理監事會推動產業發展研討會

TSIA理監事會推動產業發展研討會,由台灣半導體產業協會 (TSIA)主辦,於每季TSIA理監事聯席會議後舉行,主要針對產業界所關切之議題,透過會議交流型式,解讀當前產業局勢尋找未來出路,並凝聚產業人士之共識,形成一股推動台灣半導體產業持續前進的力量!

#### 聯誼交流

<第二回>TSIA理監事會推動產業發展研討會已於102年9月27日(星期五)晚間在新竹老爺大酒店4樓宴會廳圓滿舉行。由盧超群理事長為活動開場,歡迎貴賓們熱情參加。當前國際競爭局勢正在改變,此次跳脫本位迷思由外商角度來看台灣半導體產業競爭中之機會、威脅及優劣勢分析,特別邀請到台灣新思科技(Synopsys Taiwan)董事長葉瑞斌、安謀國際科技(ARM)總經理呂鴻祥、全球半導體聯盟(GSA)亞太區執行長王智立等分享「台灣微電子/半導體產業在全球競爭中之SWOT分析」,並邀請TSIA黃洲杰理事及唐和明理事擔任與談人,且提供實貴的意見,此次研討會座無虛席,現場討論熱烈,共計約60位公司CEO參與。

#### 聯誼交流

#### 導

#### 聯誼交流

#### TSIA盧超群理事長Opening並介紹與會貴賓

#### 專題演講貴賓

安謀國際科技(ARM) 總經理呂鴻祥先生

全球半導體聯盟(GSA) 亞太區執行長王智立博士

#### 與談交流

#### 致贈演講貴賓紀念品

### 2013 TSIA IC 設計委員會會議 暨IC設計之友夏季聯誼餐會報導

吳素敏資深經理/TSIA

現場來賓互動交流

感謝徐爵民院長、林孝平董事 新會支持

左起天新資訊陸朝中總經理 蒞會致詞、主持人吳誠文主委

TSIA IC設計委員會會議暨夏季IC設計之友聯誼會於2013年7月25日假新竹國

史歡迎廠商參與及質助聯誼曾活動: 認謝新思科技已獨家質助2013年威未設計聯誼會,預定於12月舉行,敬邀IC設計中高階主管蒞臨,有興趣參加聯誼會業界長官,請與本會秘書處聯絡。 同時尋求2014年上半年及下半年兩場次活動贊助廠商,贊助廠商可掛公司Logo於活動文宣,活動贊助廠商將依級次,有專題演講機會、蒞會致詞、邀請貴公司或客戶參加免費名額等,專題以業界有興趣之主題為主,可偏軟性題目,歡迎有興趣贊助廠商與協會聯繫(吳素敏資深經理,Tel: 03-591-3477,Email: julie@tsia.org.tw)。

主委舉杯歡迎大家蒞臨

Salesforce香港及臺灣地區 李錦安(Kevin Li)總監蒞會分享

# 半導體智財價值策略研討會活動報導

吳素敏資深經理/TSIA

去年協會針對科技公司屢屢遭受智慧財產相關訴訟的困擾,舉辦智慧財產權經營管理策略研討會,今年台灣半導體產業協會仍與台美產業合作推動辦公室(Taiwan-USA Industrial Cooperation Promotion Office, TUSA)共同合作,於9月5日(四)下午假國立交通大學(光復校區)電子資訊研究大樓第一會議廳舉行『半導體智財價值策略研討會(Semiconductor IP Value Strategies Seminar)』,共約60位業界CEOs及智財專家參與盛會。從另一角度提供業界對矽智財在其價值策略上,思考如何加強產業智財價值的建立。

本研討會以半導體產業智財的趨勢與挑戰為主軸,首先,由瑞昱半導體黃依瑋副總經理蒞會開場,以風趣的比喻點出半導體智財價值策略對台灣半導體產業發展的重要性。主題涵蓋Patent Valuation and Litigation-What Every Executive Should Know About Patent Risk、The Art and Science of Patent Valuation in a Transactional Context-Sale, Acquisition and Corporate M&A、Building Intrinsic Value of a Patent-Prosecution Perspectives等,包括邀請Gaby Khouri, Senior Director, RPX; Eric Huang, Partner, Quinn

Emanuel; Ron Laurie, Managing Director, IPS; Pejman Sharifi, Partner, Winston & Strawn等專家 分享以上智財價值議題。也特別感謝台美產業合作 推動辦公室支持本活動、TSIA IP Co-Chair 台積電 劉彥顯律師協助規劃及邀請講師、瑞昱半導體黃依 瑋副總經理暨TSIA IPWG主席蒞會主持開幕及所有邀請演講嘉賓精彩的演說及互動,使活動圓滿成 切!

最後,瑞昱半導體黃依瑋副總經理暨與會專家 參與業界來賓Panel Discussion,交互提問,相信提 供給業界許多寶貴建議,期業界更重視智財權價值 鏈的建立,佈局專利,以提升企業資產及戰鬥力。

TSIA IC設計委員會IPWG是台灣半導體產業協會會員公司之IP相關專家交流之平台,針對IC產業之IP相關需求議題,特別是世界半導體理事會(World Semiconductor Council, WSC)關心之國際IP相關議題,每年不定期召開3到5次會議及舉辦相關活動,歡迎加入協會、委員會及WG,若您對IP工作小組有興趣,歡迎與協會聯繫(吳素敏資深經理,電話:03-5913477,email:julie@tsia.org.tw)。

一會務報導·TSIA NEWS

### 台灣半導體產業 第三季回顧與展望

TSIA;工研院IEK系統IC與製程研究部

### 一、2013年第二季全球半導體市場較上季成長6.0%,較去年同期成長2.1%

據WSTS統計,13Q2全球半導體市場銷售 值達746億美元,較上季(13Q1)成長6.0%, 較去年同期(12Q2)成長2.1%;銷售量達1,774億 顆,較上季(13Q1)成長9.0%,較去年同期(12Q2) 成長3.2%;ASP為0.421美元,較上季(13Q1)衰退 2.8%,較去年同期(12Q2)衰退1.1%。

13Q2美國半導體市場銷售值達143億美元,較上季(13Q1)成長8.6%,較去年同期(12Q2)成長10.6%;日本半導體市場銷售值達82億美元,較上季(13Q1)衰退3.0%,較去年同期(12Q2)衰退20.8%;歐洲半導體市場銷售值達85億美元,較上季(13Q1)衰退0.2%,較去年同期(12Q2)成長0.8%;亞洲區半導體市場銷售值達437億美元,較上季(13Q1)成長8.3%,較去年同期(12Q2)成長5.4%。

#### 二、2013年第二季台灣IC產業產值較上 季成長16.8%,較去年同期成長14.5%

根據TSIA委託工研院產經中心(IEK)所做的調查,2013年第二季台灣整體IC產業產值(含IC設計、IC製造、IC封裝、IC測試)達新台幣4,800億元(USD\$16.2B),較上季(13Q1)成長16.8%,較

去年同期(12Q2)成長14.5%。其中IC設計業產值為新台幣1,216億元(USD\$4.1B),較上季(13Q1)成長20.2%,較去年同期(12Q2)成長20.4%;IC製造業為新台幣2,538億元(USD\$8.6B),較上季(13Q1)成長16.7%,較去年同期(12Q2)成長16.4%;IC封裝業為新台幣724億元(USD\$2.4B),較上季(13Q1)成長14.0%,較去年同期(12Q2)成長4.5%;IC測試業為新台幣322億元(USD\$1.1B),較上季(13Q1)成長12.2%,較去年同期(12Q2)成長4.2%。新台幣對美元匯率以29.6計算。

### 三、展望2013年台灣IC產業產值可達新台幣18,703億元,較2012年成長14.4%

IEK預估2013年台灣IC產業產值可達新台幣 18,703億元(USD\$63.3B),較2012年成長14.4%。

其中設計業產值為新台幣4,830億元 (USD\$16.3B),較2012年成長17.4%;製造業為 新台幣9,694億元(USD\$32.8B),較2012年成長 16.9%;封裝業為新台幣2,891億元(USD\$9.8B), 較2012年成長6.3%;測試業為新台幣1,288億元 (USD\$4.4B),較2012年成長6.0%。新台幣對美元 匯率以29.6計算。

#### 表一 2013年台灣IC產業產值

TSIA NEWS·會務報導

| 單位:億新台幣  |       |       |       |       |       |       |       |       |       |             |        |       |              |       |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------------|--------|-------|--------------|-------|

| 億新台幣     | 13Q1  | 季成長   | 年成長   | 13Q2  | 季成長   | 年成長   | 13Q3  | 季成長   | 年成長   | 13Q4<br>(e) | 季成長    | 年成長   | 2013年<br>(e) | 年成長   |

| IC產業產值   | 4,108 | -1.0% | 14.1% | 4,800 | 16.8% | 14.5% | 5,069 | 5.6%  | 15.3% | 4,726       | -6.8%  | 13.9% | 18,703       | 14.4% |

| IC設計業    | 1,012 | -5.9% | 13.1% | 1,216 | 20.2% | 20.4% | 1,338 | 10.0% | 17.9% | 1,264       | -5.5%  | 17.6% | 4,830        | 17.4% |

| IC製造業    | 2,174 | 5.4%  | 20.2% | 2,538 | 16.7% | 16.4% | 2,638 | 3.9%  | 17.8% | 2,344       | -11.1% | 13.6% | 9,694        | 16.9% |

| 晶圓代工     | 1,701 | 3.2%  | 23.2% | 1,973 | 16.0% | 17.9% | 2,050 | 3.9%  | 15.2% | 1,824       | -11.0% | 10.6% | 7,548        | 16.4% |

| 記憶體製造    | 473   | 14.3% | 10.5% | 565   | 19.5% | 11.4% | 588   | 4.1%  | 27.8% | 520         | -11.6% | 25.6% | 2,146        | 18.6% |

| IC封裝業    | 635   | -9.3% | 2.4%  | 724   | 14.0% | 4.5%  | 757   | 4.6%  | 7.1%  | 775         | 2.4%   | 10.7% | 2,891        | 6.3%  |

| IC測試業    | 287   | -8.3% | 3.6%  | 322   | 12.2% | 4.2%  | 336   | 4.3%  | 6.3%  | 343         | 2.1%   | 9.6%  | 1,288        | 6.0%  |

| IC產品產值   | 1,485 | -0.3% | 12.2% | 1,781 | 19.9% | 17.4% | 1,926 | 8.1%  | 20.8% | 1,784       | -7.4%  | 19.8% | 6,976        | 17.8% |

| 全球半導體成長率 | -     | -     | -     | -     | -     | -     | -     | -     | -     | -           | -      | -     | -            | 2.1%  |

註:(e)表示預估值(estimate)。

註:IC產業產值=IC設計業+IC製造業+IC封裝業+IC測試業。 資料來源:TSIA;工研院IEK系統IC與製程研究部(2013/08)

#### 表二 2010年至2013年台灣IC產業產值

| 單位:億新台幣      |        |              |        |                      |        |              |          |                      |

|--------------|--------|--------------|--------|----------------------|--------|--------------|----------|----------------------|

| 億新台幣         | 2010年  | 2010年<br>成長率 | 2011年  | <b>2011</b> 年<br>成長率 | 2012年  | 2012年<br>成長率 | 2013年(e) | <b>2013</b> 年<br>成長率 |

| IC產業產值       | 17,693 | 38.3%        | 15,627 | -11.7%               | 16,342 | 4.6%         | 18,703   | 14.4%                |

| IC設計業        | 4,548  | 17.9%        | 3,856  | -15.2%               | 4,115  | 6.7%         | 4,830    | 17.4%                |

| IC製造業        | 8,997  | 56.0%        | 7,867  | -12.6%               | 8,292  | 5.4%         | 9,694    | 16.9%                |

| 晶圓代工         | 5,830  | 42.8%        | 5,729  | -1.7%                | 6,483  | 13.2%        | 7,548    | 16.4%                |

| 記憶體製造        | 3,167  | 88.1%        | 2,138  | -32.5%               | 1,809  | -15.4%       | 2,146    | 18.6%                |

| IC封裝業        | 2,870  | 30.6%        | 2,696  | -6.1%                | 2,720  | 0.9%         | 2,891    | 6.3%                 |

| IC測試業        | 1,278  | 32.3%        | 1,208  | -5.5%                | 1,215  | 0.6%         | 1,288    | 6.0%                 |

| IC產品產值       | 7,715  | 39.2%        | 5,994  | -22.3%               | 5,924  | -1.2%        | 6,976    | 17.8%                |

| 全球半導體成長<br>率 | -      | 31.8%        | -      | 0.4%                 | -      | -2.7%        | -        | 2.1%                 |

註:(e)表示預估值(estimate)。

資料來源:TSIA;工研院IEK系統IC與製程研究部(2013/08)

35■ 台灣半導體產業協會簡訊 NO.66 October ■

一會務報導·TSIA NEWS

## 「IFRS實行對稅務之影響及給付國外報酬衍生之扣繳議題」 研討會活動報導

劉夢玲經理/TSIA

TSIA財委會邱垂源主委(力晶科技會計處處長)與資誠講師-蔡晏潭協理合影留念

資誠講師-蔡晏潭協理授課剪影

協助企業了解IFRS實行對稅務之影響,及在面臨中華民國來源所得扣繳議題時要如何因應,中華民國台灣半導體產業協會(TSIA)特別邀請具豐富實務經驗之資誠聯合會計師事務所蔡晏潭協理,於9月12日(四)下午,假新竹交大電資大樓第一會議室舉辦【IFRS實行對稅務之影響及給付國外報酬衍生之扣繳議題】研討會,本次研討會有95位財稅從業人員參加。

課程內容包括IFRS變革對營所稅課稅所得額之衝擊,由於國際財務會計準則(IFRS)已於2013年正式上路,IFRS 導入雖看似僅影響會計處理方式,但細究個別科目會計處理方式的不同,即可能衍生若干稅務問題。例如,首次適用IFRS導致保留盈餘變動,是否影響所得稅、未分配盈餘稅、或稅額扣抵比率的計算?實施IFRS後,跨國交易類型日趨複雜,其所涉及之中華民國來源所得是否應予扣繳之議題,在實際運作上,常出現企業與稅局認定不一的情形,而迭生爭議,即便進入訴訟程序,各行政法院的見解也有所出入,更增添適用上的困擾。蔡協理透過這次研討會的課程,與學員分享相關扣繳實務經驗。

歡迎TSIA會員公司的中高階財稅主管加入TSIA財委會;若尚未成為TSIA會員公司,亦歡迎與TSIA秘書處聯絡,了解入會辦法。TSIA秘書處聯絡人:劉夢玲經理,電話:03-591-3560,Email:ccliu@tsia.org.tw。

### TSIA委員會活動摘要

黃佳淑經理彙整/TSIA

#### 一.生產製造技術委員會

主委:聯華電子-許堯壁處長

- 102年6月17日召開e-Manufacturing & Design Collaboration Symposium 2013午餐會議,討論 研討會籌備現況、贊助現況與計畫。

- 102年6月24日舉辦廠商座談會簡介e-Manufacturing

& Design Collaboration Symposium 2013活動內容、BigDate Special Session計畫及贊助辦法。

- 102年7月8日召開e-Manufacturing & Design Collaboration Symposium 2013第九次籌備會 議,討論贊助現況、議程安排、經費計畫、文宣 計畫、IEEE接洽狀況等。

- 102年7月24日召開e-Manufacturing & Design Collaboration Symposium 2013第十次籌備會議,討論贊助現況、議程安排、經費計畫、文宣計畫、IEEE接洽狀況、BigData規劃與講師等。

- 102年8月9日召開e-Manufacturing & Design Collaboration Symposium 2013第十一次籌備會議,討論贊助現況、議程安排、經費計畫、文宣計畫、IEEE接洽狀況、BigData規劃與講師及貴賓邀請計畫等。

- 102年8月20日召開e-Manufacturing & Design Collaboration Symposium 2013第十二次籌備會議,討論稿件回收現況、Proceedings CD製作、報名現況、Session Chair安排等。

- 102年8月26日召開e-Manufacturing & Design

- Collaboration Symposium 2013午餐,討論eMDC運作基金、與ISSM合作計畫等。

- 102年9月4-6日與SEMI擴大合辦SEMICON Taiwan 2013,盧理事長代表TSIA開幕致詞,並 於晚宴與吳副總統同台致詞,獲滿堂彩及副總統 讚許。

- 102年9月5日召開e-Manufacturing & Design Collaboration Symposium 2013第十三次籌備會議,討論稿件回收狀況、Proceedings CD製作、與會人員現況、研討會會議室、午餐、晚宴及場佈等。

- 1 0 2 年 9 月 6 日 於 新 竹 國 賓 飯 店 主 辦 e-Manufacturing & Design Collaboration Symposium 2013,約260人與會。

- 102年9月12日召開e-Manufacturing & Design Collaboration Symposium 2013檢討會議,討論會 場現況、與ISSM合作計畫及2014年計畫日期等。

#### 二.IC設計委員會

主委: 工研院資通所-吳誠文所長

- 102年7月10日召開JEDEC Post Meeting,並改選CEMIF工作小組召集人及副召集人,分別由聯發科宣敬業經理及晶豪科技蕭子哲處長當選。

- 102年7月25日舉辦TSIA IC設計委員會暨IC設計 之友夏季聯誼餐會,由天新資訊獨家白金贊助。

- 102年8月15與JEDEC於新竹國賓飯店合辦「Mobile Forum Taiwan 2013」, Samsung,

Qualcomm, ARM, Micron, Toshiba, Synopsys,

37■ 台灣半導體產業協會簡訊 NO.66 October ■

Arasan, Agilent等國內外60幾家相關廠商蒞會發表JEDEC最新標準及趨勢,約300人與會。

- 102年9月5日舉辦半導體智財經營管理策略研討會,提供國際級的智財價值策略,對台灣業界有很大的助益。

- 102年9月9-13日參加於美國Austin召開之JEDEC

國際標準制定會議,由華邦電子邱濱棋經理及聯發科宣敬業經理代表出席參加。

- 102年9月24日於工研院4樓國際會議廳與市場資訊委員會聯合舉辦智慧車用與醫療電子應用技術發展與市場趨勢研討會。

- TSIA半導體相關短期在職培訓課程,至9月15日前已開辦3班,培訓71人次。

#### 三.技術藍圖委員會

主委:台積電-Carlos H. Diaz處長

- 102年7月8-9日於美國舉行之2013 ITRS IRC / ITWG夏季會議,由台積電Carlos H. Diaz處長、 京元電子陳文如資深處長及旺宏電子劉瑞琛副總 經理代表協會出席參加。

- 102年8月9日與工研院合辦2013 ITRS AP Roadmap & 3D IC Technology Development Workshop。

#### 四.市場資訊委員會

主委:華邦電子-林正恭副總經理

- 102年8月14日發佈2013第三季TSIA IC產業動態調查季報及中英文新聞稿。

- 102年9月24日於工研院4樓國際會議廳與IC設計委員會聯合舉辦智慧車用與醫療電子應用技術發展與市場趨勢研討會。

- 籌備規劃102年11月18-21日於台北晶華酒店舉行 WSTS秋季市場預測會議相關事宜。

- 2014 WSC/JSTC/TFs Meeting將於103年5月份

於台北圓山飯店舉行。WSC Market Committee 將由瑞昱半導體黃依瑋副總經理擔任主席,Committee將支持例行Market Report暨Special Market Report,計畫將以台灣半導體產業,特別是晶圓代工及設計的成功經驗導入,感謝台積電支持晶圓代工部分,設計公司已拜會聯發科尋求支持。

#### 五.財務委員會

主委: 力晶科技-邱垂源處長

102年9月12日於國立交通大學電資大樓第一會議室,與資誠聯合會計師事務所合辦「IFRS實行對稅務之影響及給付國外報酬衍生之扣繳議題」研討會,特別邀請具豐富經驗實務經驗之蔡晏潭協理擔任講師,本次研討會共有90位財稅從業人員參加。

#### 六. 環保安全衛生委員會

主委:台積電-許芳銘處長

- 102年7月3日召開環安委員會「2013年第三次委員會議及CEMS功能小組研商會議(7)」。

- 102年7月17日CEMS測試程序小組針對「修正「公私場所固定污染源揮發性有機物監測設施性能規範參考原則」半導體製造業空氣污染管制及排放標準」召開工作小組會議。

- 102年7月19日許芳銘主委拜訪財團法人安全衛生技術中心于樹偉董事長,針對職業安全衛生法和毒管法修法內容交換意見並提出業界需求與建言。

- 102年7月22日CEMS測試程序小組針對「修正「公私場所固定污染源揮發性有機物監測設施性能規範參考原則」半導體製造業空氣污染管制及排放標準」拜訪環保署黎科長。

- 102年7月24日CEMS測試程序小組針對「修正「公私場所固定污染源揮發性有機物監測設施性能規範參考原則」半導體製造業空氣污染管制及排放標準」拜訪環保署空保處謝處長。

- 102年7月29日許芳銘主委、丁立文、殷伊嫻、黃中一、呂慶慧代表等出席環保署召開之「公私場所固定污染源揮發性有機物監測設施性能規範參考原則草案」研商暨公聽會議。

- 102年8月6日許芳銘主委、丁立文、殷伊嫻、黃中一、呂慶慧代表等出席環保署召開之「溫室氣體空氣污染防治費徵收規劃座談會」。

- 102年8月9日許芳銘主委、丁立文、殷伊嫻、黃中一、呂慶慧代表等出席環保署召開之「公私場所固定污染源揮發性有機物監測設施性能規範參考原則草案」第二次研商暨公聽會議。

- 102年8月12日許芳銘主委、丁立文、殷伊嫻、 黃中一、呂慶慧代表等出席工業局召開之因應 「公私場所固定污染源申報空氣污染防制費之揮 發性有機物之行業製程排放係數、操作單元〈含 設備元件〉排放係數、控制效率及其他計量規定 修正」第二次討論會議。

- 102年8月19日賴懷仁委員參加WSC ESH

Committee Chemical WG電話會議。

- 102年8月21日許芳銘主委召開並主持WSC ESH Committee Resource Conversation WG電話會 議。

- 102年8月23日許芳銘主委等針對「毒性化學物質管理法」拜訪環保署環境衛生及毒物管理處謝鄭春菊科長。

- 102年8月27日許芳銘主委、丁立文、殷伊嫻、 黃中一、呂慶慧代表等出席環保署召開之「溫室 氣體排放標準(或效能標準)規劃溝通會」。

- 102年9月5日許芳銘主委接受天下專訪「空氣污染與疾病,探討國內空污所帶來的問題」專題。

- 102年9月13日與經濟部能源局、中華民國大氣層保護協會共同主辦「高科技產業能源與環境保護國際研討會」。

- 102年9月23-25日由許芳銘主委率領賴懷仁、羅明廉、呂慶慧、石英堂等代表出席於韓國濟州島召開之WSC ESH Committee會議。

#### 七.產學委員會

主委:交通大學-吳重雨教授

- 102年7月8日由吳重雨主委召開並主持「TSIA 產學委員會成立會議」,討論產學界委員之招 募計劃、半導體發展主軸計劃白皮書之推動計 劃、校園演講等議題。

- 102年8月15日由吳重雨主委召開並主持 「TSIA推動產學合作活動會議」,由全體委員 共同參加,針對半導體發展主軸計劃白皮書之 推動計劃,成立3個工作小組;並針對校園演 講之各種合作模式進行評估與討論。會中並提 出成立產學基金的構想,以支付日後產學合作 計劃所需要之費用。

- 102年9月27日由闕志達副主委與潘正聖副主委召開「TSIA產學委員會臨時會議」, 了解半導體發展主軸計劃白皮書之執行現況並決議於102年10月14日召開「TSIA產學委員會工作小組會議」。

### 新會員介紹

編輯部

#### 愛普科技股份有限公司 AP Memory Technology Corp.

#### 公司概況:

愛普科技自民國100年8月4日成立,一直以來 致力於PSRAM設計研發與銷售。近期拓展至DDR1 與DDR2之設計研發。主要為手機或平板Buffer Memory之應用。

#### 公司產品:

- 1. Known Good Dies pSRAM / Cellular RAM—Cell Phone

- 2. Stand Alone pSRAM Memory—Low Power SRAM Application

- 3.Embedded pSRAM Solution—Low Cost Embedded SRAM Solution

#### 勤友企業股份有限公司 Kingyoup Enterprises Co., Ltd.

#### 公司概況:

自1974年創立以來,勤友秉持著誠信與負責的態度,代理歐、美、日等國的精密工具、量測設備、光學儀器,非破壞性檢測系統、半導體檢測設備、液晶面板製造檢查設備、及環保設備等,以至2006年開始著手自行研發、設計大型連續式真空濺鍍設備,為觸控面板業界龍頭廠商所採用。

長年投入於製造、工業檢測的產品應用,不僅 累積量測技術的know how,更需因應市場趨勢,持 續開發新產品以回應客戶需求,並努力增進研發團 隊實力、掌握先進的製程技術,以提升企業整體競 爭力。近40年來,除台北總公司外,於新竹、台中、台 南、高雄、大陸蘇州太倉等地設立服務據點。

#### 公司產品:

代理歐、美、日工業檢測設備、Hitachi液晶面板製造檢查設備;近年投入連續式真空濺鍍設備的設計與製造,已為觸控業界認證採用;現並積極開發半導體業相關製程設備。

公司網址:www.kingyoup.com

#### 聯亞科技股份有限公司 United Industrial Gases Co., Ltd

#### 公司概況:

1988年聯華氣體向竹科半導體廠提出管線供應的構想,邀請台積電、聯電、華邦、旺宏、華微等主要半導體廠共同成立聯亞科技。聯華氣體則是由Linde集團及聯華實業股份有限公司共同投資設立,是台灣最大的工業氣體製造商。透過與遍布全球Linde集團公司的密切合作,聯華氣體能夠提供不同種類的各種高品質氣體和氣體應用技術。為配合迅速的成長,聯華氣體在高效率的氣體生產設備上投資了相當龐大的金額。

#### 公司產品:

- 1.生產及銷售液氧、液氮、液氮、氮氧、液氮、氮 氣、液氮、超高純度氧、超高純度氮、超高純度 氬、超高純度氫、稀有氣體氖、氪、氙、高純度液 態二氧化碳、氧化亞氮以及前述各項氣體應用設備 等項產品。

- 2. 銷售氫氣。

- 3. 前項產品製造、銷售之研究發展、技術諮詢及售後服務。

公司網址:www.boclh.com.tw/tw/about/ divisions/index.html

#### 馗鼎奈米科技股份有限公司 Creating Nano Technologies Inc.

#### 公司概況:

植鼎奈米科技股份有限公司之技術團隊在電漿 領域的研發已有十餘年的歷史,在國內對於電漿技 術的開發位於領導的地位,目前已是國內最大常壓 電漿設備生產製造商,其產品穩定性深獲國內面板 大廠肯定,有效提升面板生產之良率及信賴度。

本公司具有全世界首屈一指的電漿與鍍膜專業技術,專長於IC、光電與通訊製程技術與設備的研發。客戶領域鎖定在光電(液晶顯示器,有機發光二極體)、半導體(如IC,電子封裝)、印刷電路板、精密機械(模具,工具鍍膜)、光纖通訊、微機電等產業,提供未來快速成長的電子資訊產業關鍵技術。

#### 公司產品:

- 1.各式鍍膜代工(類鑽炭、鑽石、氧化鈦、鉻、 鋁…等)

- 2.電漿清潔機生產製造販賣

- 3.電漿去膠渣機生產製造販賣

- 4.水滴接觸角生產製造販賣

- 5.微氧分析儀生產製造販賣

- 6.大氣電漿清潔機生產製造販賣

- 7.其他電漿技術應用相關產品(如PVD鍍膜機、CVD 鍍膜機)

公司網址:www.creating-nanotech.com/

#### 漢民微測科技股份有限公司 Hermes Microvision Inc.

#### 公司概況:

漢民微測自成立於1998年以來就致力於研發最先進的電子束檢測技術來協助提升半導體產業之良率。目前漢民微測已經成為世界各大晶圓代工廠與晶圓記憶體廠最大的電子束檢測設備供應商。我們擁有自行研發專利的電子槍技術、電子束成像技術與精準的檢測軟體,來確保我們的每條產品線-eScan®系列、ePTM系列、eXplore®系列皆能滿足半導體研發部門與量產單位之各項應用。

#### 公司產品:

- 1.半導體設備製造

- 2.全球製程整合服務

公司網址:http://www.hermes-microvision.com/ch/

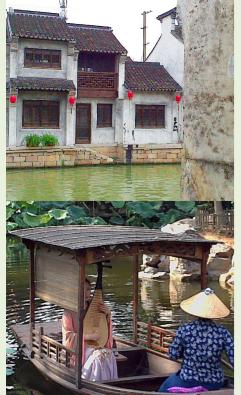

→ 里鶯啼綠映紅,水村山郭酒旗風;南朝四百八十 寺,多少樓台煙雨中。」杜工部一首七絕,短短二 十八個字,嵌盡春和景明、南國煙波,描摹出桃花源的印象、也 刻劃著捕魚人的嚮往;李瑞洵曾在為林俊傑填的詞中唱道:「雨 到了這裡纏成線,纏著我們流連人世間。」或許就是這樣一絲絲 對長江以南這片樂土的迤邐懷想,才會不知不覺跟著哼著「風到 這裡就是黏,黏住過客的思念。」正是恰如其分的時機和緣份分 秒不差地剛剛好碰上了,才在那性情中人張禮部所謂的「一江煙 水照清嵐。兩岸人家接畫檐工季節,有幸乘著芰荷與沙鷗舞過的 風,親自養一回浩然之氣,體會是什麼樣的境況,孰能令人「愛 殺江南」。

抵達南京,望向無垠的無涯處,天空盡是一張工業大城的 網,撈遍這座都市天際的藍,取而代之成為陰霾罩頂的灰。踏 入中山陵,自牌坊而後羅列有致的林蔭和來到此地彼此心照不宣 的肅穆氛圍隨著層層臺階拾級而上。那不是如坐針氈的畏懼, 而是一股,呼吸著這片林木的芬多精,就彷彿增加更多腦內啡-般——愉悦、且自然而然油然而生肅然起敬的情感。若由上空俯 視整座陵寢,會驚覺原來它的輪廓竟是一只鐘,簡中蘊藏了國父 孫逸仙博士期望「喚醒民眾」的深切冀盼。

搭著小巴奔馳過幾條筆直公路,地陪兀自地滔滔不絕介紹 著,那横跨長江的宏偉鋼樑大橋已然映入眼簾,無怪乎得獎者總 謙稱: 越接近偉大時更顯得自己的渺小。我就像偶然撞見格列佛 的村民,在龐然大物之前讚嘆人類工藝文明的壯麗;走進橋下展

覽室,舊文物陳述著創業維艱的歷史軌跡; 抬頭看到毛澤東左右兩塊匾額分別刻著: 「團結起來,爭取更大的勝利!」跟「全世 界人民大團結萬歲!」領略了些,牛頓感謝 巨人肩膀和童話裡螞蟻經常扮演團隊合作代 言人的理念。

隔天轉往無錫造訪三國影視城,夏日炎 炎,本來嘛華中、華南一帶,火傘免不了高 張,還記得為那天少帶了點防曬油與太陽眼 鏡懊悔不已,而從遠處傳來了喧嘩聲,從那 達達的腳步聲聽來,鐵定不是歸人,想著自 個兒同是盤桓個幾天便轉身離開的觀光客 放寬心,也放過了自己。

還記得讀過蘇東坡見黃州赤壁遙想公瑾當年,小喬初嫁了,雄姿 英發,羽扇綸巾;當我們坐在央視替年度古裝大戲搭的舞台佈景之中 欣賞著--虎牢關前看三英戰呂布,再乘上東吳水軍一流的快艇,追憶 諸葛孔明是如何草船借箭、黃蓋又怎麼火燒連環船,「老兵不死,只 是凋零。」五零年代麥克阿瑟將軍被解職後發表的著名演講,在這現 代人造出緬懷當年的場景中,隨著沙場馬蹄揚起的塵土一揮,忒也拂 進胸懷。

輾轉到了蘇州,相信拜張懿孫之賜,不少人對「姑蘇城外寒山寺」 並不陌生。就是這首楓橋夜泊,儘管張繼本人流傳後世的作品不多,-首千古絕唱,便足以將他的姓名烙在古稱妙利普明塔院之牆上,永垂不 朽。大概即因聲名太盛,遊人如織,當初南梁寒山與唐朝詩人的空靈今 卻已不復見;兜售紀念品的小販很多、鼎沸的人聲很旺,互謀其利無不 可,只是保存的古蹟已然隨斑駁的院壁飄零了許多況味,備感神傷。

椅墊還沒坐熱,在蘇州閶門外不是很遠的地方,須臾間司機大哥又 踩了剎車——留園,跟同處蘇州的拙政園、北京的頤和園、承德的避暑 山莊並稱中國的四大名園。園內利用建築群對各景點進行分隔,同時透 過窗欞將景物相聯,並建造麯廊連接全園各部。曲廊隨勢而變,時攀山 腰,時畔水際,逶迤曲折,全長七百餘米。廊壁鑲嵌劉恕收集的歷代碑 刻三百餘方,稱「留園法帖」,其中尤以王羲之、王獻之父子的「二王 法帖」最為人稱道;假山奇石,峰迴路轉,「瑞雲峰」更有「妍巧甲於 江南」之美譽。但最得我心的,莫非藉引莊子與惠施論辯「汝安之魚之 樂」的牌匾。凝視水波粼粼和上頭的陽光燦燦、聆賞歌女的琵琶錚錚。 看著、看著不禁微醺,醉倒在這無邊無際古今交錯的迷幻中

最後一天來到西湖龍井問茶,在此之前先去了趟西溪溼地國家公園,舒淇與葛優的賣座電影——非誠勿擾的背景之一。待到了梅家塢, 負責領我們杭州行程的導遊請製茶師傅露了一手選茶和沏茶的好功夫, 細細品聞龍井清香、靜靜觀賞特意挑過的透明玻璃杯中緩緩柔順展開的 茶葉,眉頭不再緊皺、釋放笑顏好像沒那麼難。「岐王宅裡尋常見,崔 九堂前幾度聞。正是江南好風景,落花時節又逢君。」走在風華絕代的 南宋御街上,洋樓及老字號店鋪相偎相依,胡慶餘堂、胡雪巖故居跟現 代感十足的速食店比鄰而立……在一家賣古玩意兒的雜貨商流連了幾許時 光,佇立於店外的玻璃櫥窗猛然回首時,驚鴻一瞥……倘若來年,千里相 逢一念間,「日出江花紅勝火,春來江水綠如藍,能不憶江南?」

### TSIA入會申請資格及辦法

歡迎申請加入TSIA台灣半導體產業協會,請至TSIA網站http://www.tsia.org.tw 於「入會申請」專區留言或 e-mail 到 service@tsia.org.tw,我們將儘速與您聯絡!

| 會員   |                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 團體會員 | 凡設籍中華民國之半導體產業相關機構(研發、設計、製造、構裝、測試、設備、材料),設計類資本額超過(含)新台幣一億元,晶圓製造、封裝、測試、光罩等類資本額超過(含)新台幣兩億元,設備、零組件、材料類等資本額超過(含)新台幣四億元,並在台灣設廠者,填具入會申請書,經理事會審核通過,並繳納會費後,成為會員,並依據所繳常年會費數額推派代表二至三十人行使會員權益。 |

| 國際會員 | 凡總公司設於中華民國境外之半導體產業相關機構(研發、設計、製造、<br>構裝、測試、設備、材料),在台灣設立分公司、辦事處或研發中心,<br>填具入會申請書,經理事會審核通過,並繳納會費後,成為會員。                                                                               |

| 贊助會員 | 捐助本會之團體,並經本會理事會通過後,得為贊助會員。                                                                                                                                                         |

| 榮譽會員 | 由理事會推薦頒贈。                                                                                                                                                                          |

| 會費   |          |                                      |                                                                     |               |  |  |

|------|----------|--------------------------------------|---------------------------------------------------------------------|---------------|--|--|

| 入會費  | 會員(榮譽    | 會員除外)於本會時,應一次                        | 總納入會費新台幣 1 萬元整                                                      |               |  |  |

|      |          | 資本額 (新台幣/元)                          | 常年會費/年                                                              | 得派代表人數        |  |  |

|      |          | 二億以下                                 | 2萬元                                                                 | 2人            |  |  |

|      |          | 二億(含)~四億                             | 4萬元                                                                 | 3人            |  |  |

|      | 團體會員     | 四億(含)~十億                             | 6萬元                                                                 | 4人            |  |  |

|      | <b>一</b> | 十億(含)~三十億                            | 12萬元                                                                | 6人            |  |  |

|      |          | 三十億(含)~一百億                           | 18萬元                                                                | 8人            |  |  |

|      |          | 一百億(含)~五百億                           | 32萬元                                                                | 12人           |  |  |

|      |          | 五百億(含)以上                             | 90萬元                                                                | 30人           |  |  |

| 常年會費 |          | 級數 定義(根據加入會                          | 會員時之前一年度排名)                                                         | 常年會費/年(新台幣/元) |  |  |

|      | 國際會員     | A 全球前二十大半導體<br>IBM, Philips, ST, Fre | 豊公司如Intel, TI, Samsung,<br>eescale, Sony等                           | 60 萬元         |  |  |

|      |          | NVDIA等,及各國/b                         | B 全球前二十大IC公司如Qualcomm, Broadcom, NVDIA等,及各國/地區前十大半導體相關公司,非屬於全球前二十大者 |               |  |  |

|      |          | С                                    | 其他                                                                  | 5 萬元          |  |  |

|      | 贊助會員     | 每年新台幣 2 萬元整                          |                                                                     |               |  |  |

|      |          |                                      |                                                                     |               |  |  |